# ZnO-based metal-semiconductor field-effect transistors

Von der Fakultät für Physik und Geowissenschaften der Universität Leipzig genehmigte

DISSERTATION

zur Erlangung des akademischen Grades Doctor rerum naturalium Dr. rer. nat.

vorgelegt von

Dipl.-Phys. Heiko Frenzel geboren am 4. November 1981 in Leipzig

Gutachter: Prof. Dr. M. Grundmann (Universität Leipzig) Prof. Dr. T. Riedl (Bergische Universität Wuppertal)

Tag der Verleihung: 18. Oktober 2010

# **Bibliografische Beschreibung**

Frenzel, Heiko ZnO-based metal-semiconductor field-effect transistors Universität Leipzig, Dissertation 149 Zitate, 86 Abbildungen, 26 Tabellen

#### Referat:

Die vorliegende Arbeit befasst sich mit der Entwicklung, Herstellung und Untersuchung von ZnO-basierten Feldeffekttransistoren (FET). Dabei werden im ersten Teil Eigenschaften von einund mehrschichtigen Isolatoren mit hohen Dielektrizitätskonstanten betrachtet, die mittels gepulster Laserabscheidung (PLD) dargestellt wurden. Die elektrischen und kapazitiven Eigenschaften dieser Isolatoren innerhalb von Metall-Isolator-Metall (MIM) bzw. Metall-Isolator-Halbleiter (MIS) Übergängen wurden untersucht. Letzterer wurde schließlich als Gate-Struktur in Metall-Isolator-Halbleiter-FET (MISFET) mit unten (backgate) bzw. oben liegendem Gate (topgate) genutzt. Der zweite Teil konzentriert sich auf Metal-Halbleiter-FET (MESFET), die einen Schottky-Kontakt als Gate nutzen. Dieser wurde mittels reaktiver Kathodenzerstäubung (Sputtern) von Ag, Pt, Pd oder Au unter Einflußvon Sauerstoff hergestellt. ZnO-MESFET stellen eine vielversprechende Alternative zu den bisher in der Oxid-basierten Elektronik verwendeten MISFET dar. Durch die Variation des verwendeten Gate-Metalls, Dotierung, Dicke und Struktur des Kanals und Kontakstruktur, wurde ein Herstellungsstandard gefunden, der zu weiteren Untersuchungen herangezogen wurde. So wurde die Degradation der MESFET unter Belastung durch dauerhaft angelegte Spannung, Einfluss von Licht und erhöhten Temperaturen sowie lange Lagerung getestet. Weiterhin wurden ZnO-MESFET auf industriell genutztem Glasssubstrat hergestellt und untersucht, um die Möglichkeit einer großflächigen Anwendung in Anzeigeelementen aufzuzeigen. Einfache integrierte Schaltungen, wie Inverter und ein NOR-Gatter, wurden realisiert. Dazu wurden Inverter mit sogenannten Pegelschiebern verwendet, welche die Ausgangsspannung des Inverters so verschieben, dass eine logische Aneinanderreihung von Invertern möglich wird. Schließlich wurden volltransparente MESFET und Inverter, basierend auf neuartigen transparenten gleichrichtenden Kontakten demonstriert.

"We are stuck with technology when what we really want is just stuff that works."

- Douglas Adams, The Salmon of Doubt (2002)

Summary of the scientific results of the dissertation

ZnO-based metal-semiconductor field-effect transistors

submitted by

Dipl.-Phys. Heiko Frenzel

prepared at

Fakultät für Physik und Geowissenschaften der Universität Leipzig Institut für Experimentelle Physik II, Abteilung Halbleiterphysik June 2010

# 1 Introduction

The present thesis deals with the design, development and investigation of ZnO-based field-effect transistors (FET) for the use in future transparent electronics (TE). Transparent electronics have become a fast-growing field in semiconductor physics and material science due to its comprehensive applications in, e.g., transparent displays in windows and as transparent flat-panel TVs, invisible electronics in functional furniture or dishes, and augmented-reality devices. The key active devices for TE are transparent field-effect transistors (TFET), which are necessary as pixel-driver, for logic integrated circuits and memories. They are up to now mostly implemented as metal-insulator-semiconductor field-effect transistors (MISFET) consisting of a transparent semiconductor channel, a dielectric gate oxide and transparent contacts. As channel material, usually ZnO and ZnO-based amorphous oxides such as gallium indium zinc oxide (GIZO) or zinc tin oxide (ZTO) are used [1]. The gate dielectrics are usually oxides with high dielectric constants (high- $\kappa$ ) such as aluminium oxide, titanium oxide, zirconium oxide, hafnium oxide and mixed crystalls thereof. Indium tin oxide and degenerately doped ZnO:Al are used as transparent contacts.

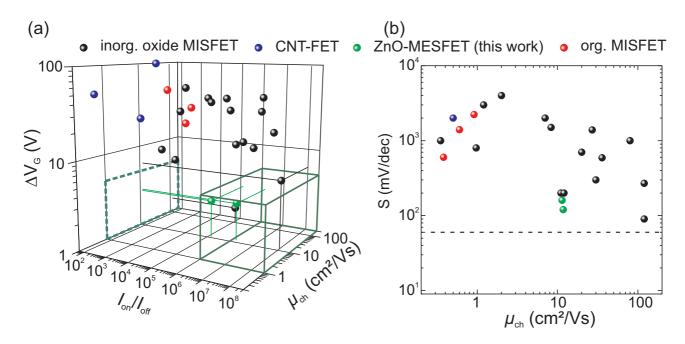

The figures of merit for FET are: the ratio between the source-drain currents in the on- and in the off-state (on/off-ratio), the gate-voltage sweep needed for the given on/off-ratio, the channel mobility, and the subthreshold slope representing the logarithmic gain. For display applications, Wager recommended an on/off-ratio of >  $10^6$ , a channel mobility >  $1 \text{ cm}^2/\text{Vs}$ , and a device transmission of 70% [2]. For the implementation of TFET into integrated circuits (IC), a gate-voltage sweep < 5 V and a subthreshold slope < 200 mV/decade are additionally recommended [3].

Oxide MISFET and related IC usually suffer from high operating voltages due to the voltage drop across the insulator and limited switching speed due to the reduced channel mobility. The channel mobility of MISFET is reduced compared to the Hall-effect mobility of the used semiconductor due to scattering of carriers at the insulator/semiconductor interface [4]. Therefore, the issues for the fabrication of MISFET are the reduction of the insulator thickness and the reduction of interface defects under perpetuation of the insulating properties.

The main focus of this thesis is the realization of ZnO-thin-film-based metal-semiconductor fieldeffect transistors (MESFET) comprising a Schottky contact as gate. Due to the missing insulator and insulator/semiconductor interface, MESFET exhibit much lower operating voltages than MISFET and a higher channel mobility that ideally equals the semiconductor's Hall-effect mobility [5]. The MESFET presented in this thesis are a promising alternative approach to common MISFET based TE.

ZnO-thin-film MESFET were previously demonstrated by Ryu *et al.*, who used Ti as gate contact on *p*-type ZnO [6]. Kandasamy *et al.* used Pt-gate n-ZnO MESFET for hydrogen gas sensing [7]. Kao *et al.* used Pt/Au gate-contacts for their MESFET [8]. All reported thin-film ZnO MESFET show inferior electronic properties with high gate-voltage sweeps between 4 and 20 V, very low on/off-ratios below 1 decade and barely obtained pinch-off and saturation behavior in the output. On the basis of ZnO nanorods, MESFET and logic devices such as OR, AND, NOT, and NOR-gates have been realized by Park *et al.* using Au-gate contacts [9]. Their on/off-ratio was  $\sim 10^4$  and a subthreshold slope between 100 and 200 mV/decade was achieved. Channel mobilities were neither reported for ZnO thin-film nor nanorod MESFET.

# 2 Pulsed-laser-deposited metal-insulator-semiconductor field-effect transistors

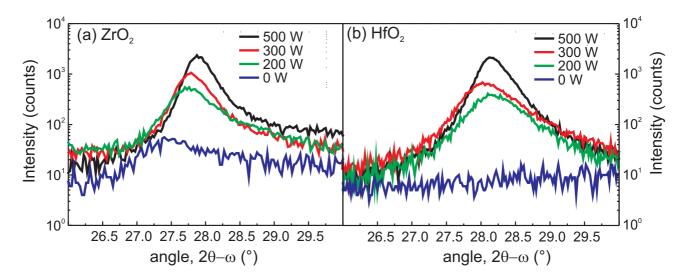

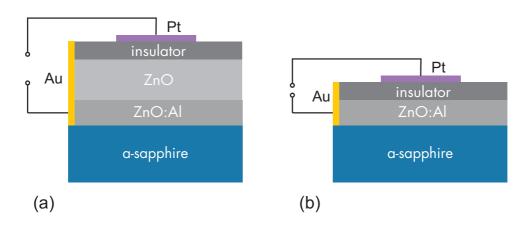

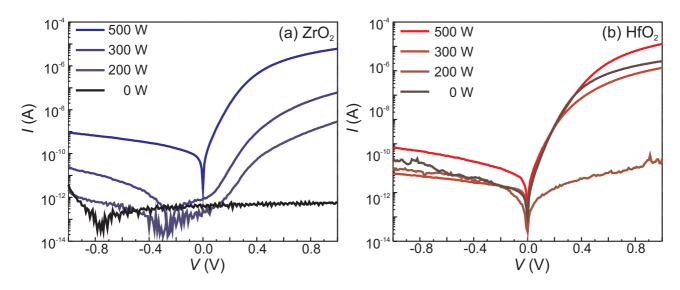

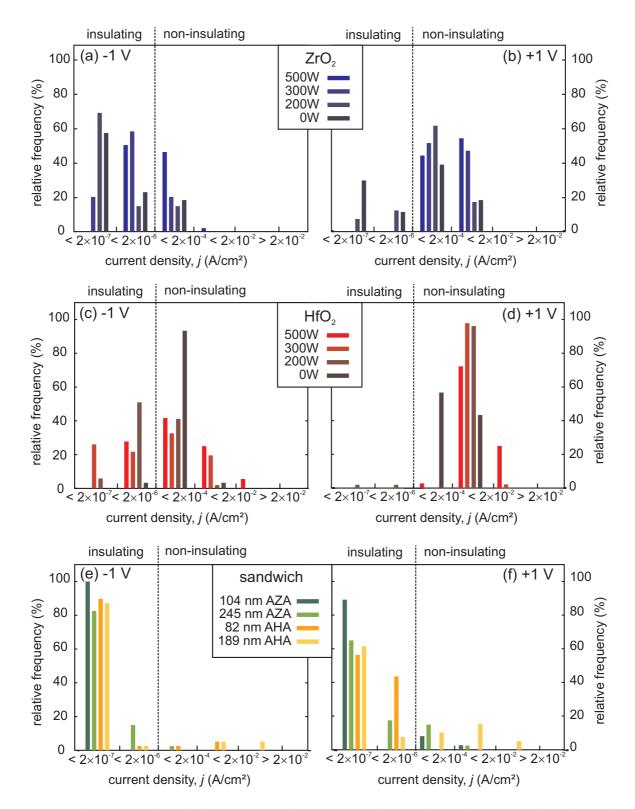

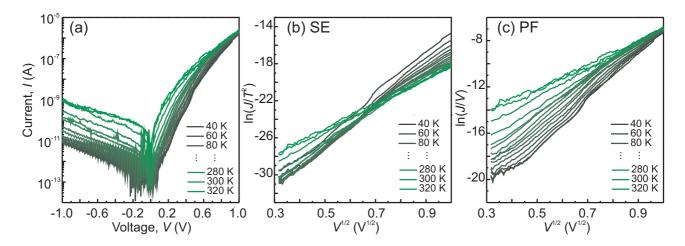

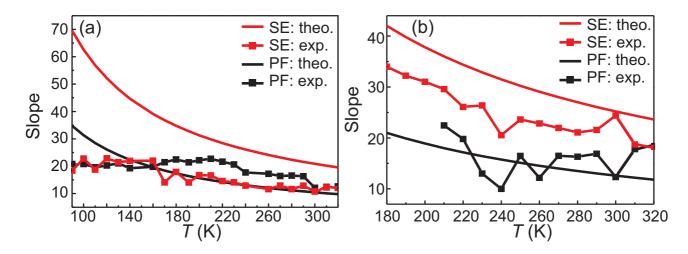

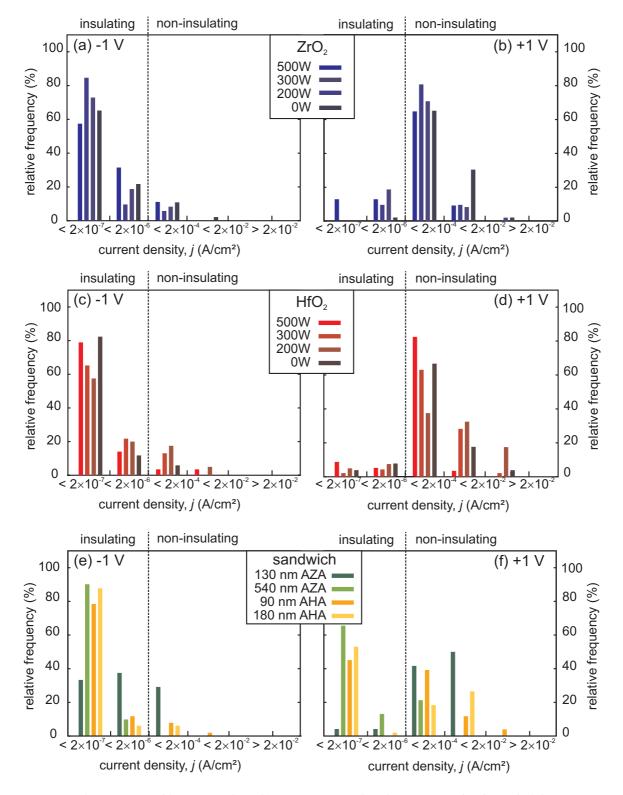

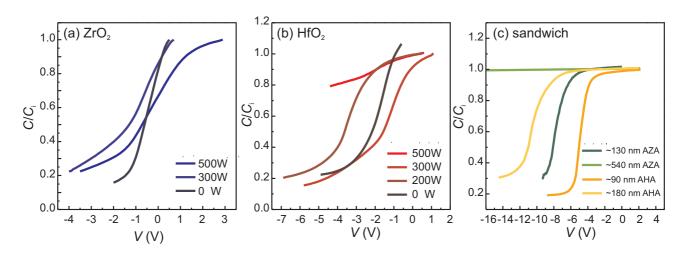

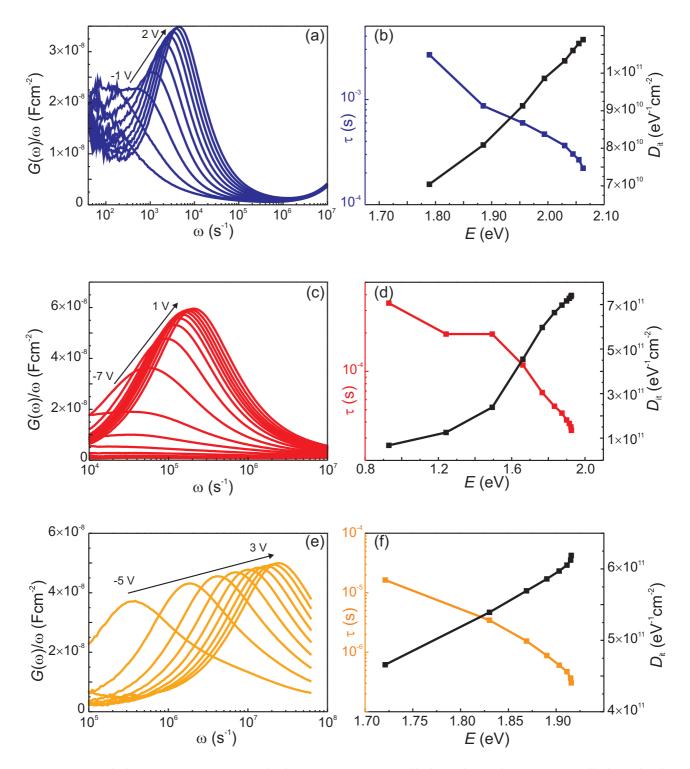

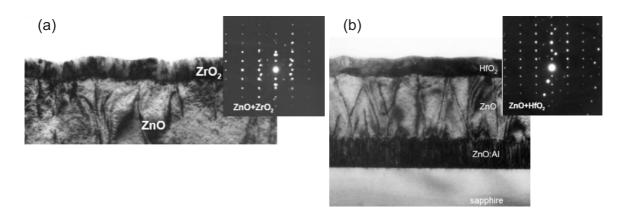

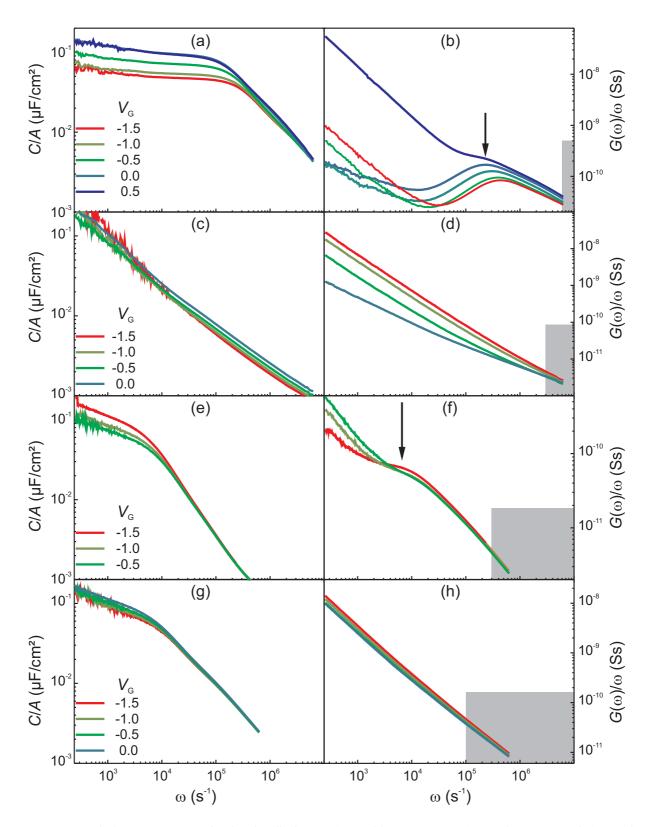

For the reduction of MISFET operating voltages, high- $\kappa$  insulators are needed. In this thesis,  $ZrO_2$ , HfO<sub>2</sub> as well as Al<sub>2</sub>O<sub>3</sub>-ZrO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> sandwich-layer insulators are grown by pulsed-laser deposition (PLD) and investigated by means of current-voltage (IV) and capacitancevoltage (CV) measurements within metal-insulator-metal (MIM) and metal-insulator-semiconductor (MIS) structures. The insulators grown at different substrate heater powers did not show a clear tendency. All insulators exhibit forward conduction for positive applied voltages at the Pt frontcontact. Up to 80% of the contacts with  $ZrO_2$  or  $HfO_2$  are insulating for -1 V (leakage current density  $< 2 \times 10^{-6}$  Acm<sup>-2</sup>) but only 15% of the contacts are insulating at +1 V. For the sandwich-structure insulators, 80-100% (60-80%) of the contacts are insulating at -1 V (+1 V). The lower leakage currents can be explained by the higher band offset between  $Al_2O_3$  and ZnO. The different material interfaces form a diffusion barrier for mobile ions. Temperature-dependent IV measurements reveal that the most probable mechanisms for the observed forward conduction are Schottky emission and Poole-Frenkel emission, indicating less importance of shunts and grain boundaries. The dielectric constants obtained from quasi-static CV measurements (QSCV) are in good agreement with the literature for the MIM structures and lay in the range between 13 for  $HfO_2$  (13–16 [10]) and 25 for  $ZrO_2$  (20–25 [11]). For the MIS diodes on ZnO, the highest  $\kappa$ -values are achieved for the highest substrate heater power and exceeded 33 for both  $HfO_2$  and  $ZrO_2$ . QSCV measurements also reveal an excess of positive charges, i.e. metal, within the insulators, which may form defects that are responsible for the observed forward conduction. The amount of these charges is found to be a factor of 10 to 20 lower for sandwich insulators than for single-layer insulators.

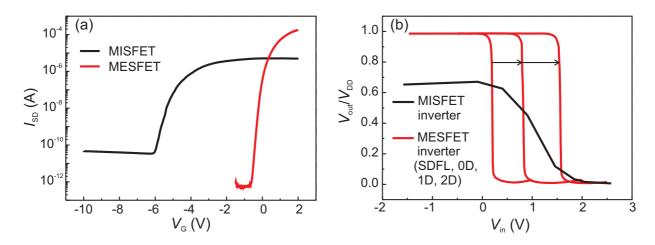

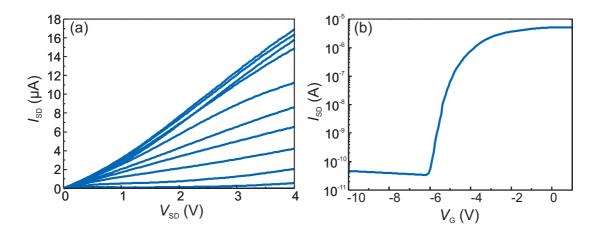

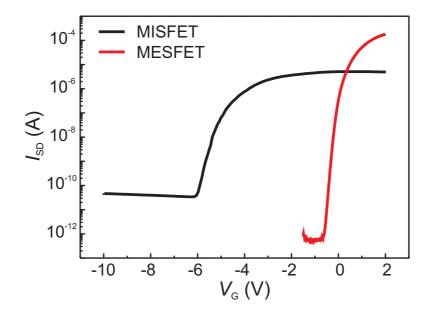

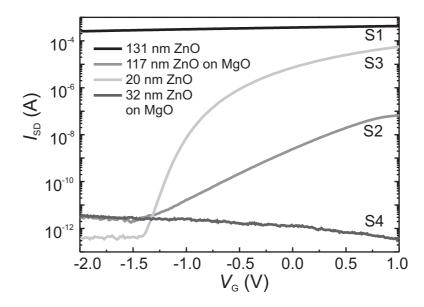

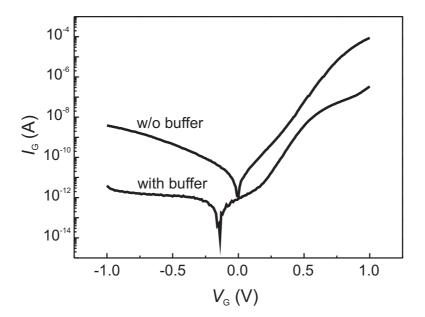

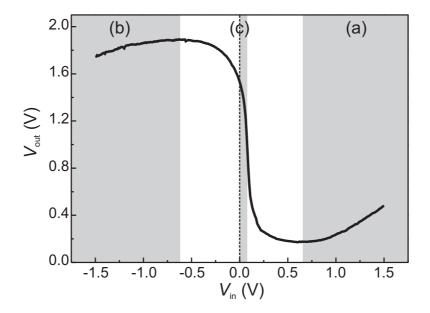

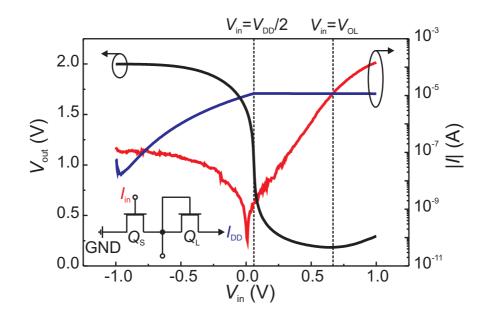

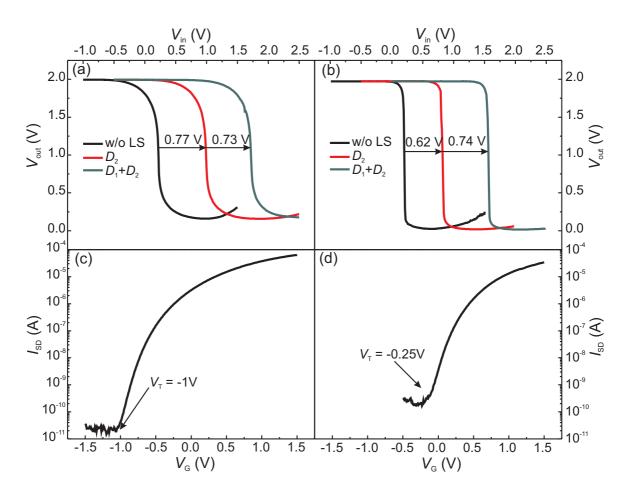

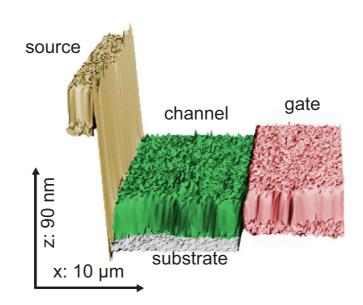

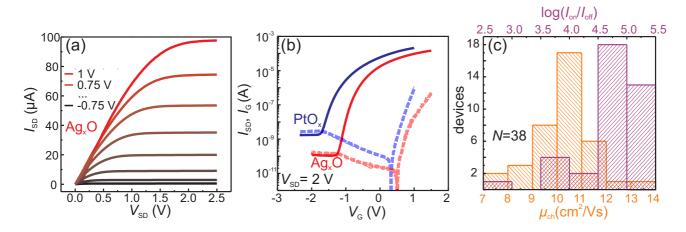

A top-gate ZnO-MISFET with a 90 nm thick  $Al_2O_3$ -HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> sandwich-insulator is fabricated [12]. Its transfer characteristic is compared with a typical ZnO-MESFET on sapphire in Fig. 1a. The normally-on MISFET exhibits a turn-on voltage of -6 V and the source-drain current can be tuned over five orders of magnitude within a gate-voltage sweep of only 7 V. The minimum subthreshold slope of 300 mV/decade is among the best reported ZnO-MISFET. However, the channel mobility of  $1.9 \text{ cm}^2/\text{Vs}$  is a factor of ten lower than the Hall-effect mobility, which can be attributed to scattering at interface-trap charges. The interface-trap charge density was measured by admittance spectroscopy and lay in the range of  $10^{11}-10^{12} \text{ cm}^{-2} \text{eV}^{-1}$ , which is similar to other reported values for these insulators [13].

For the bottom-gate ZnO MISFET, a more than 800 nm thick  $Al_2O_3$  layer is necessary to reduce the leakage currents below  $10^{-10}$  A at  $\pm 60$  V. A comparison is made between *a*-plane and *r*-plane sapphire substrates. Both MISFET show normally-on behavior with turn-on voltages between -40and -50 V. The on-current, on/off-ratio and channel mobility is higher for the *r*-plane MISFET due to its higher free-carrier concentration. Here, the diffusion of donors in to the ZnO-channel seems to be more likely. Compared to the top-gate MISFET, the channel mobilities of the bottom-gate MISFET are significantly lower  $(0.3 \text{ cm}^2/\text{Vs}$  and  $0.5 \text{ cm}^2/\text{Vs}$  for *a*-plane and for *r*-plane sapphire, respectively). Similar channel mobilities were also observed for a bottom-gate MISFET using an equally grown ZnO channel and a ferroelectric BaTiO<sub>3</sub>-insulator on SrTiO<sub>3</sub> substrate [14].

Figure 1: a) Transfer characteristics of the best MISFET realized within this thesis and a typical MESFET with W/L = 21.5. b) Voltage-transfer characteristics of a MISFET-based inverter from [23] and a MESFET-SDFL inverter of this thesis with zero, one and two Schottky diodes as level-shifter.

# 3 ZnO-based metal-semiconductor field-effect transistors

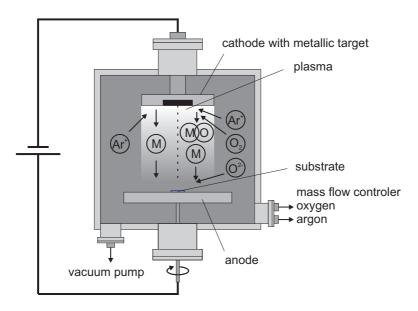

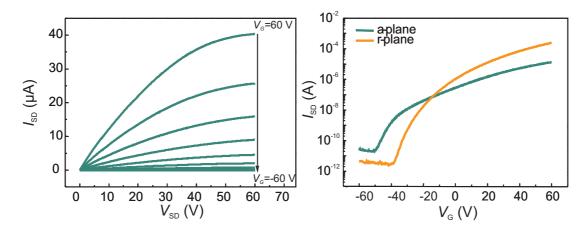

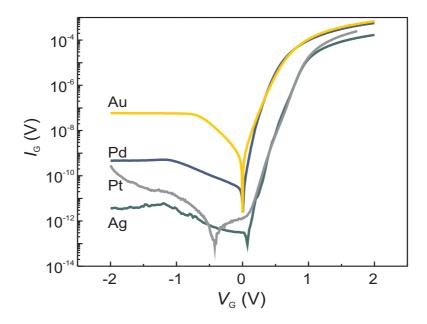

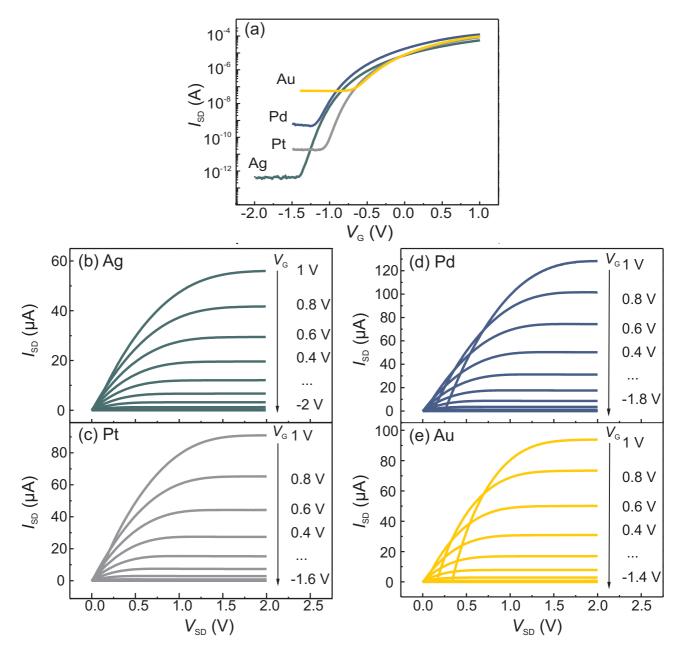

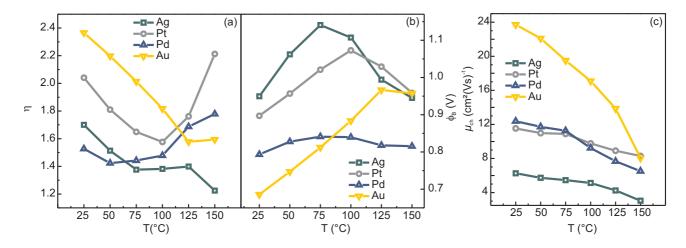

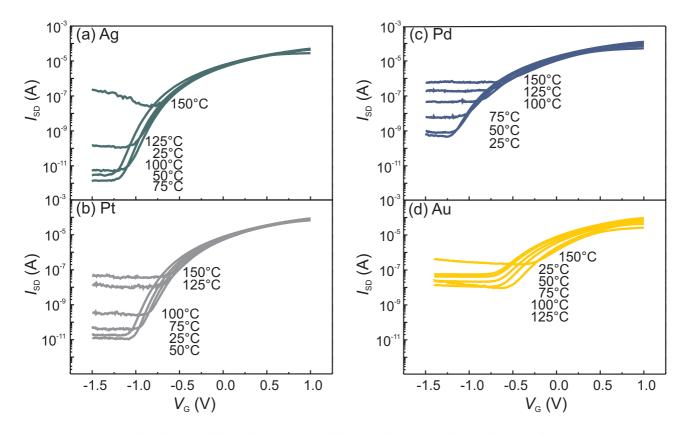

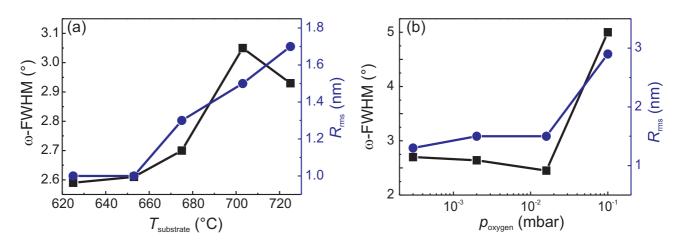

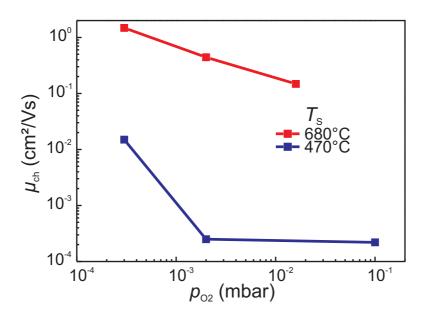

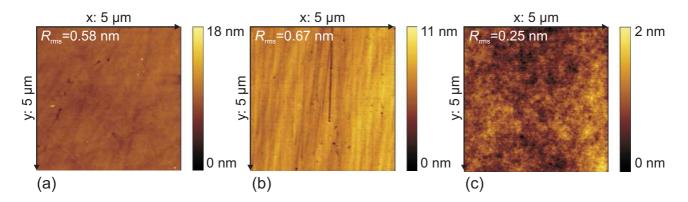

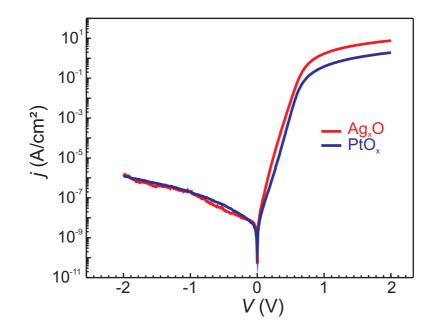

ZnO-based MESFET are fabricated using highly rectifying Schottky contacts deposited by means of reactive dc-sputtering of Ag, Pt, Pd or Au on thin ZnO channels. It has been shown by Lajn et al., that, except of Au, the metals are partially oxidized on ZnO thin films [15]. The dominant transport mechanism is similar to metallic Schottky contacts thermionic emission and their Schottky barrier heights are increased compared to pure metals. For reactively sputtered Schottky contacts on ZnO single-crystals, this has been reported by Allen *et al.* [16, 17]. For the MESFET-gate diodes, the Schottky barrier heights are as high as 0.95 V, 0.90 V, 0.79 V and 0.69 V for Ag, Pt, Pd and Au, respectively [18]. For thin films on sapphire substrate, all possible design parameters for ZnO-MESFET are varied: gate material, channel thickness and doping, gate geometry as well as channel mobility [19]. A standard configuration is found using  $Ag_xO$  as gate on a nominally undoped, 20 to 30 nm thick ZnO channel without buffer layer. With that, an on/off-ratio of  $10^8$  and a channel mobility  $> 10 \,\mathrm{cm^2/Vs}$  is achieved within a gate-voltage sweep of only 3 V. [5]. The minimum slope of  $\sim 80 \,\mathrm{mV/decade}$  is already close to the thermodynamic limit of  $60 \,\mathrm{mV/decade}$  for FET operating at room-temperature. The highest channel mobility for the standard configuration is  $27 \,\mathrm{cm}^2/\mathrm{Vs}$ . It is shown that the channel mobility of the ZnO-MESFET is usually equal to the respective Hall-mobility, which is the major advantage of MESFET compared to MISFET. However, leakage currents may lead to the underestimation of the channel mobility.

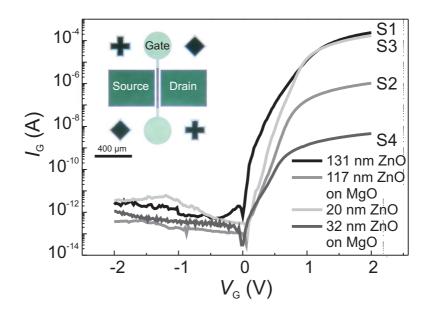

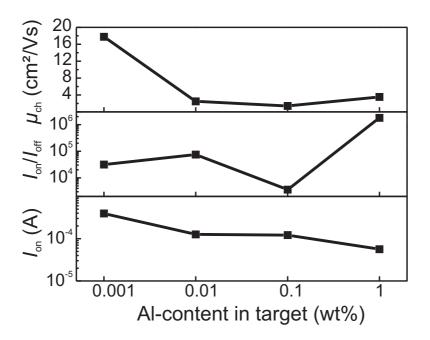

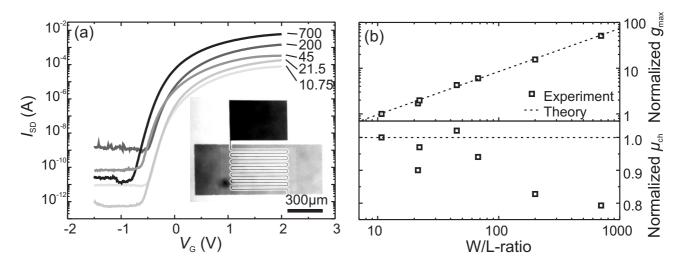

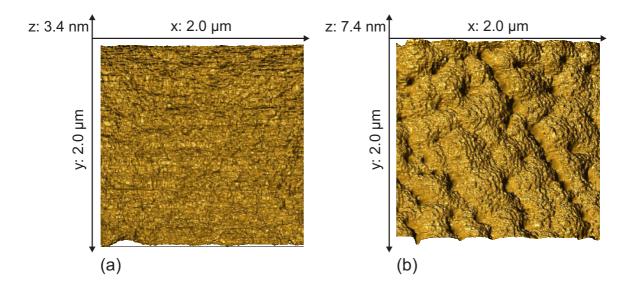

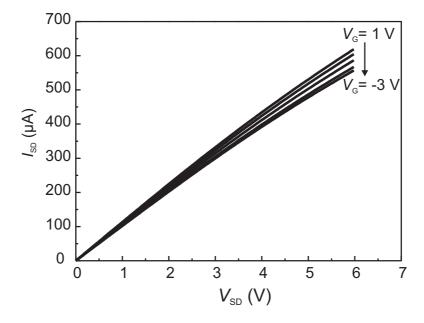

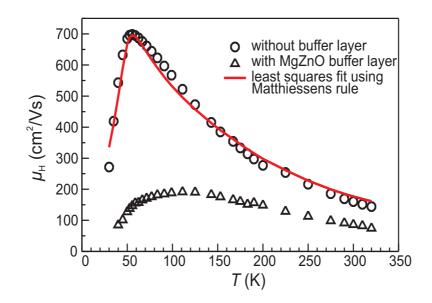

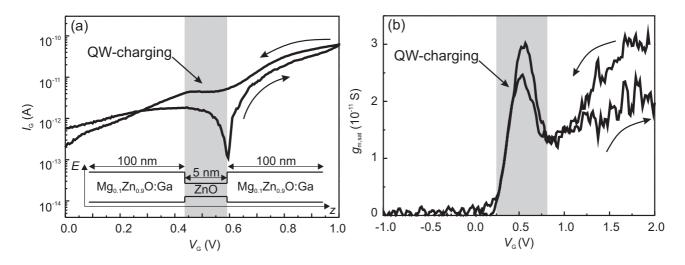

MESFET with Ag<sub>x</sub>O and PtO<sub>x</sub> gates show similar electrical performances. Ag<sub>x</sub>O is used as standard, because the MESFET exhibited lower leakage currents and higher stability at elevated temperatures. By means of a MgO-buffer layer between sapphire substrate and a nominally undoped ZnO-channel, the net doping concentration in the channel is reduced from ~  $10^{18}$  cm<sup>-3</sup> to  $10^{14}$  cm<sup>-3</sup> due to the reduced diffusion of Al from the sapphire. Based on that, it is possible to intentionally dope the channel. A reduced doping concentration leads to a reduced scattering on charged impurities. However, the variation of the Al-content in ZnO-targets between 0.001 wt-% and 1 wt-% led again to doping concentrations in the high  $10^{18}$  cm<sup>-3</sup>-range and excessive leakage currents. Increasing the thickness of the undoped ZnO-channel to ~ 120 nm on MgO-buffer results in a decreased on/off-ratio of ~  $10^4$  compared to the standard configuration due to the lower on-current. The highest on-current of 15 mA and on/off ratio of  $5 \times 10^8$  is achieved using an interdigitated contact geometry with a gate width-to-length-ratio of 700 making the MESFET suitable for applications as pixel-driver transistors for active-matrix LCD or OLED displays [20]. An increase of the MESFET channel mobility up to  $50 \text{ cm}^2/\text{Vs}$  is achieved by the improvement of the channel crystal quality using homoepitaxially grown ZnO [12]. However, these MESFET have shown insufficient saturation behavior due to parasitic currents through the ZnO substrate and their channel mobility is underestimated by a factor of three compared to the Hall-effect mobility. A further way to increase the channel mobility is demonstrated using a quantum-well (QW) structure. The formation of a two-dimensional electron gas in the MgZnO/ZnO/MgZnO-QW is observed at a gate voltage of 0.5 V. In the same voltage range, a peak-like increase of the channel transconductance is observed, which is directly related to the channel mobility.

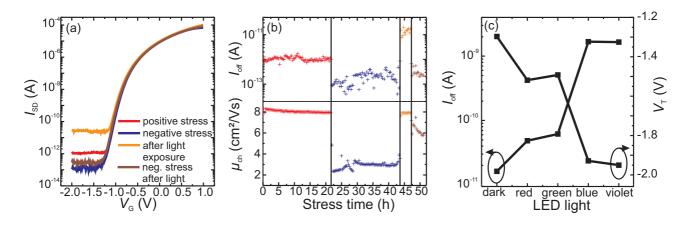

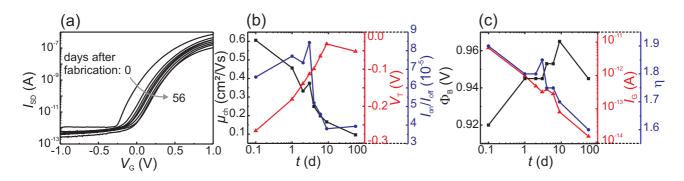

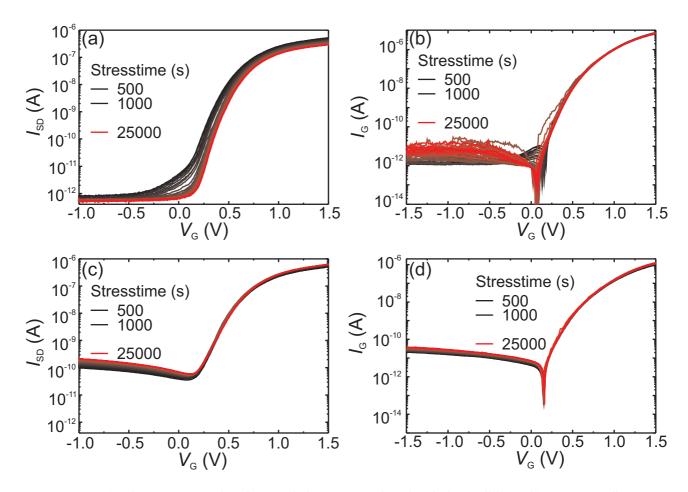

Reliability and degradation effects of the MESFET are investigated at elevated temperatures, under the exposure to visible light, by means of bias stress and long-term stability measurements. The MESFET with  $Ag_xO$  and  $PtO_x$  gates are stable until temperatures of 100°C and 75°C, respectively, without showing a significant increase in off-current or turn-on-voltage shift [18]. Temperatures above these values result in irreversible degradation of the MESFET. Bias stress measurements on the MESFET reveal no influence of interface charges, i.e. under positive or negative gate-voltage stress over a period of 22 hours, no turn-on voltage shift is observed, which represents a major advantage of MESFET compared to MISFET. An influence of visible light on the off-current and the turn-on voltage is observed for blue and violet light. The maximum turn-on voltage shift under irradiation of violet light is 0.65 V compared to shifts between 2 V and 20 V for amorphous-channel MISFET [21].

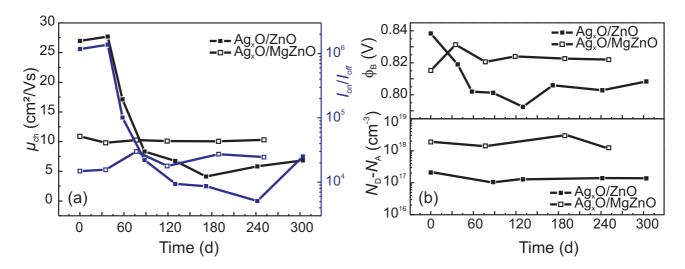

Long-term stability measurements show a decrease of the channel mobility and on/off-ratio for the ZnO-channel MESFET after 100 days before they stay constant [19]. Using ZnO-channels with a small amount (0.25%) of Mg leads to lower initial values that are, however, constant for the whole periode of 300 days. It is further observed that the reproducibility of the MgZnO-MESFET is higher than for ZnO-MESFET.

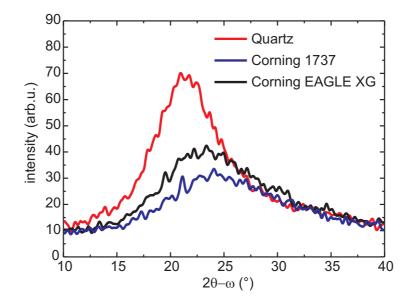

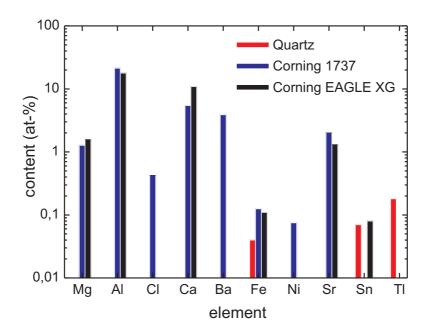

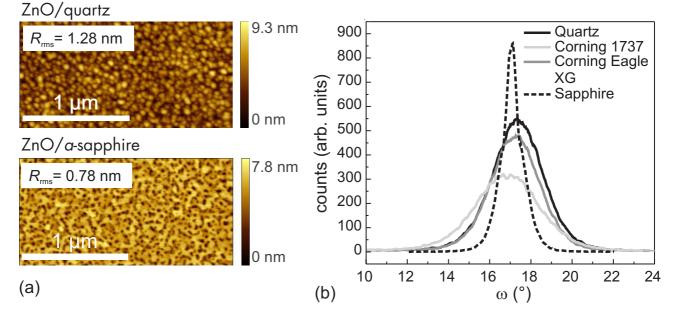

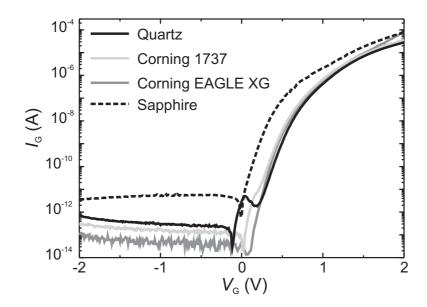

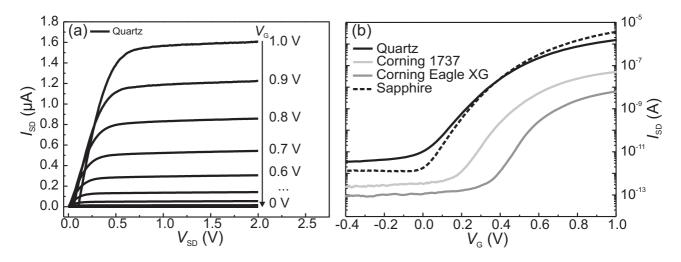

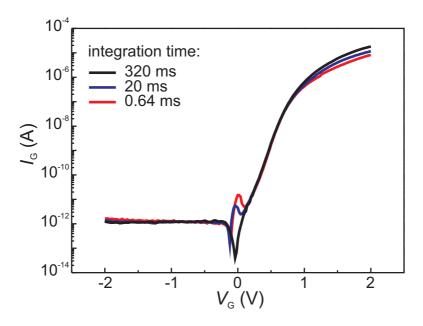

ZnO-MESFET are fabricated on industrially more relevant glass substrates. For that, a ZnO target with 0.01 wt-% Al and an oxygen partial pressure of  $3 \times 10^{-4}$  mbar is used aberrant from the standard configuration for sapphire substrate. A comparison of MESFET on quartz glass and on two commercial borosilicate substrates show a significant difference in the channel conductivity [22]. All MESFET on glass are normally-off due to compensation by indiffusion of elements such as Li, Na, K, B from the substrate into the channel. A broad distribution of defects is observed by means of admittance spectroscopy. The highest channel mobility of  $1.3 \text{ cm}^2/\text{Vs}$  and on/off-ratio of  $4.7 \times 10^5$  is achieved for quartz. The MESFET on sapphire, a fast degradation of the electrical properties for MESFET on quartz glass is observed already within a periode of 10 days. The turn-on voltage, on/off-ratio and channel mobility decrease, whereas the Ag<sub>x</sub>O-gate Schottky barrier height increases. This implies an alteration of the oxidation of the gate material. During bias stress measurements, a small turn-on voltage shift of 0.2 V is observed under dark conditions, which is, however, assigned to the reduction of an initially photogenerated charge at the gate/channel interface. Under permanent illumination, those charges are not observed.

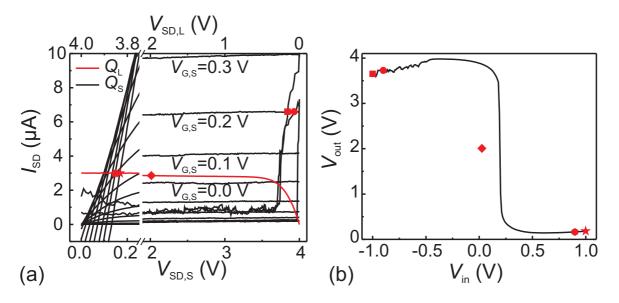

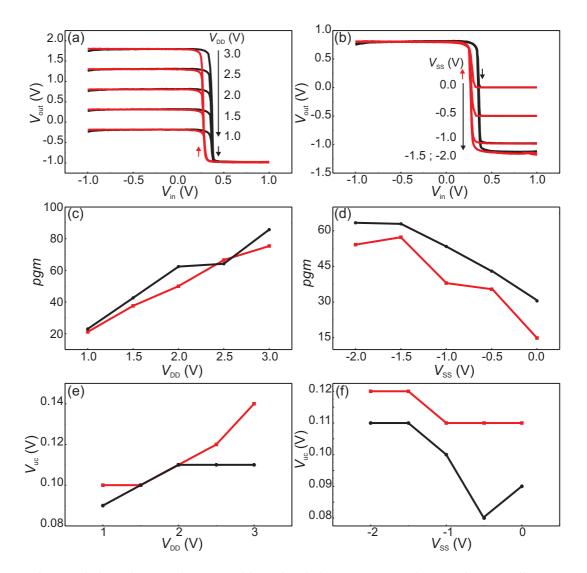

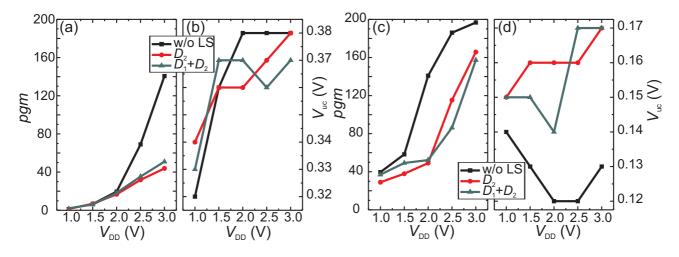

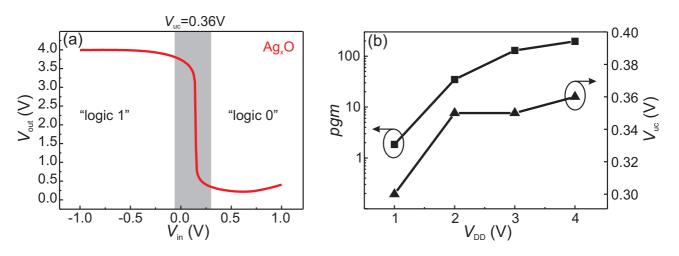

## 4 Inverter

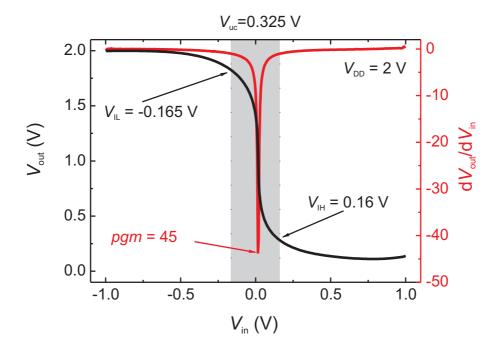

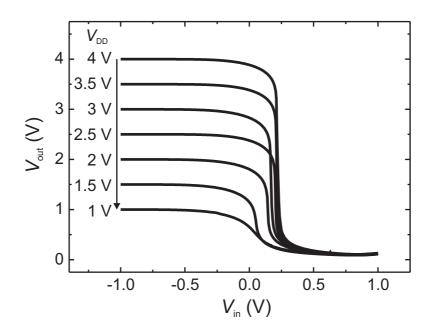

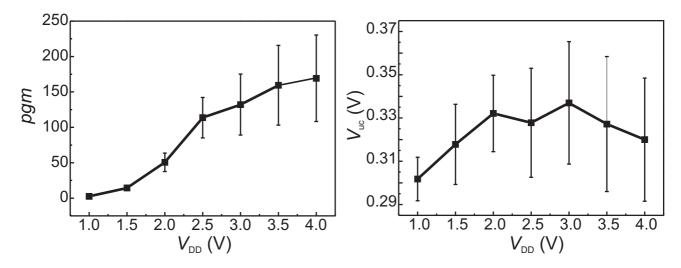

Based on ZnO-MESFET technology developed within this thesis, integrated logic circuits are fabricated. Three types of inverters: simple inverter, FET-logic (FL) inverter and Schottky-diode FET-logic (SDFL) inverter are investigated. With the simple inverter, consisting of two normally-on MESFET, the peak gain magnitude can be tuned in the range between 2.5 at an operating voltage of 1 V and 250 at 4 V; the uncertainty level stays constant at  $\sim 0.3$  V. These values are superior to comparable ZnO-MISFET inverters [23] (cf. Fig. 1b). Deviations of the real inverter characteristics from the ideal one are related to leakage and breakdown currents of the switching transistor for the high-output and low-output deviation, respectively. The positive switching-point deviation is assigned to charge trapping at the gate/channel-interface.

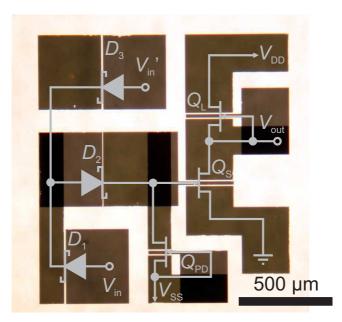

The principle of a level shifter consisting of Schottky diodes and an additional MESFET at the

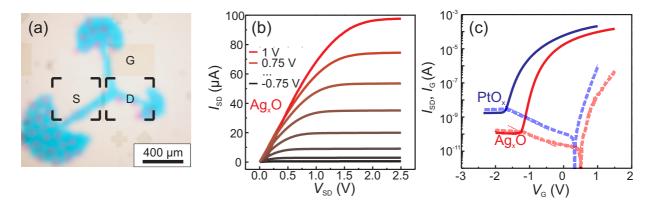

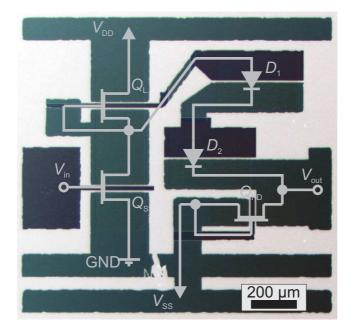

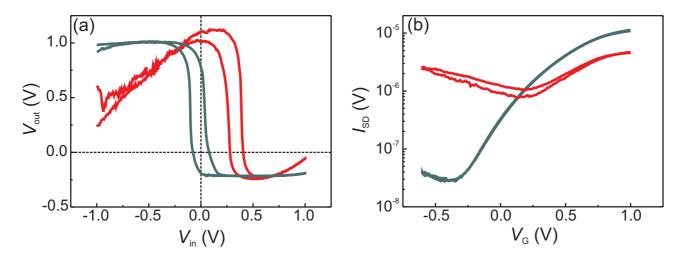

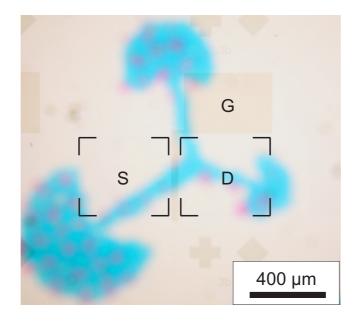

Figure 2: a) Microscopic image of a transparent MESFET, Background: printed logo of the graduate school "BuildMoNa" on a transparency. b) Output characteristics of a transparent MESFET with  $Ag_xO$ . c) Transfer and gate characteristics of transparent MESFET with  $Ag_xO$  and  $PtO_x$ .

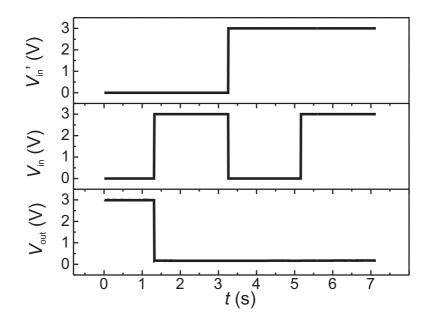

output side (FL) or input side of the inverter (SDFL) is demonstrated for the ZnO-MESFET inverters. This is adapted from commonly known GaAs MESFET technology [24]. For the FL-inverter, the output-voltage is shifted up to -1.2 V at a pull-down voltage of -1.5 V. The uncertainty level is reduced to  $\sim 0.1$  V, which is similar to GaAs inverters. Using the SDFL-inverter, the influence of the switching transistor turn-on voltage on the voltage-transfer curve is investigated [25]. For the lower negative turn-on voltage of the switching transistor, the inverter achieves a higher peak gain magnitude of 197 and the lower uncertainty level of 0.13 V at 3 V operating voltage, whereas it is only 141 and 0.37 V, respectively, for the higher negative turn-on voltage. The input-voltage is shifted by 1.5 V with two additional Schottky diodes. Connecting a third diode at the input of the inverter, a NOR-gate is implemented.

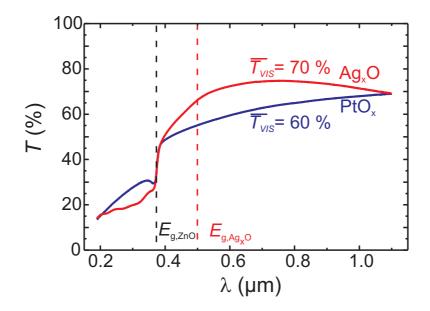

## 5 Transparent rectifying contacts

For the realization of fully transparent ZnO-MESFET electronics, transparent rectifying contacts (TRC) are developed and demonstrated within Schottky diodes, MESFET and inverters [3]. A patent application has been filed [26]. The contacts consist of the ZnO-channel layer, an ultrathin (~ 5 nm) transparent Ag<sub>x</sub>O or PtO<sub>x</sub> layer and an equally thin highly conductive oxide or metal as capping layer. The overall transmission of the complete device structure is 70% and 60% for Ag<sub>x</sub>O and PtO<sub>x</sub>, respectively. The Schottky diodes show excellent rectifying behavior with an ideality factor of only 1.47, a maximum barrier height of 0.87 V and the reverse leakage currents at -2V were as low as  $10^{-6}$  A/cm<sup>2</sup>. The fully transparent MESFET and inverters exhibit similar electrical properties as the presented opaque devices. With an on/off-ratio of  $1.4 \times 10^6$ , a channel mobility of  $2 \text{ cm}^2/\text{Vs}$  and a maximum gate-voltage sweep of 3 V, (Fig. 2) as well as a peak gain magnitude of ~ 200 and an uncertainty level of 0.36 V for the MESFET and the inverters, respectively, the devices are among the best reported transparent transistors or inverters of any kind.

# References

- M. Grundmann, H. Frenzel, A. Lajn, M. Lorenz, F. Schein, and H. von Wenckstern, Proc. E-MRS 2009 Spring Meeting Symposium F, phys. stat. sol. (a), 207 (6), 1437 (2010).

- [2] J. F. Wager, Science **300** (5623), 1245 (2003).

- [3] H. Frenzel, A. Lajn, H. von Wenckstern, and M. Grundmann, J. Appl. Phys. 107, 114515 (2010).

- [4] B. V. Zeghbroeck, *Principles of semiconductor devices*, online (2004), http://ecewww.colorado.edu/ bart/book/book/index.html.

- [5] H. Frenzel, A. Lajn, M. Brandt, H. von Wenckstern, G. Biehne, H. Hochmuth, M. Lorenz, and M. Grundmann, Appl. Phys. Lett. 92(19), 192108 (2008).

- [6] Y. R. Ryu, T. S. Lee, J. A. Lubguban, H. W. White, Y. S. Park, and C. J. Youn, Appl. Phys. Lett. 87(15), 153504 (2005).

- [7] S. Kandasamy, W. Wlodarski, A. Holland, S. Nakagomi, and Y. Kokubun, Appl. Phys. Lett. 90(6), 064103 (2007).

- [8] C. J. Kao, Y. W. Kwon, Y. W. Heo, D. P. Norton, S. J. Pearton, F. Ren, and G. C. Chi, J. Vac. Sci. Technol. B 23(3), 1024.

- [9] W. Park, J. Kim, G.-C. Yi, and H.-J. Lee, Adv. Mater. 17(11), 1393 (2005).

- [10] J.-H. Hong, T.-H. Moon, and J.-M. Myoung, Microelectron. Eng. **75**(3), 263 (2004).

- [11] M.-S. Kim, Y.-D. Ko, J.-H. Hong, M.-C. Jeong, J.-M. Myoung, and I. Yun, Appl. Surf. Sci. 227(1-4), 387 (2004).

- [12] H. Frenzel, H. von Wenckstern, A. Lajn, M. Brandt, G. Biehne, H. Hochmuth, M. Lorenz, and M. Grundmann, PHYSICS OF SEMICONDUCTORS: 29th International Conference on the Physics of Semiconductors 1199(1), 469 (2010).

- [13] G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. 89(10), 5243 (2001).

- [14] M. Brandt, H. Frenzel, H. Hochmuth, M. Lorenz, M. Grundmann, and J. Schubert, J. Vac. Sci. Technol. B 27, 1789 (2009).

- [15] A. Lajn, H. von Wenckstern, Z. Zhang, C. Czekalla, G. Biehne, J. Lenzner, H. Hochmuth, M. Lorenz, M. Grundmann, S. Wickert, C. Vogt, and R. Deneke, J. Vac. Sci. Technol. B 27(3), 1769 (2009).

- [16] M. W. Allen, S. M. Durbin, and J. B. Metson, Appl. Phys. Lett. **91**(5), 053512 (2007).

- [17] M. W. Allen, R. J. Mendelsberg, R. J. Reeves, and S. M. Durbin, Appl. Phys. Lett. 94(10), 103508 (2009).

- [18] H. Frenzel, A. Lajn, H. von Wenckstern, G. Biehne, H. Hochmuth, and M. Grundmann, Thin Solid Films 518(4), 1119 (2009).

- [19] H. Frenzel, A. Lajn, H. von Wenckstern, M. Lorenz, F. Schein, Z. Zhang, and M. Grundmann, Adv. Mater. published online, DOI:10.1002/adma.201001375 (2010).

- [20] M. Grundmann, H. Frenzel, A. Lajn, H. von Wenckstern, F. Schein, and M. Lorenz, Mater. Res. Soc. Symp. Proc. 1201, H01 (2010).

- [21] P. Görrn, M. Lehnhardt, T. Riedl, and W. Kowalsky, Appl. Phys. Lett. **91**(19), 193504 (2007).

- [22] H. Frenzel, M. Lorenz, A. Lajn, H. von Wenckstern, G. Biehne, H. Hochmuth, and M. Grundmann, Appl. Phys. Lett. 95(15), 153503 (2009).

- [23] J. Sun, D. A. Mourey, D. Zhao, and T. N. Jackson, J. Electron. Mater. **37**(5), 755 (2008).

- [24] A. S. Sedra and K. C. Smith, *Microelectronic Circuits* (Oxford University Press, 2004), 5th ed.

- [25] H. Frenzel, F. Schein, A. Lajn, H. von Wenckstern, and M. Grundmann, Appl. Phys. Lett. 96(11), 113502 (2010).

- [26] H. Frenzel, A. Lajn, H. von Wenckstern, and M. Grundmann, Transparente gleichrichtende Metall-Metalloxid-Halbleiterkontaktstruktur und Verfahren zu seiner Herstellung und Verwendung, German Patent No. 10 2009 030 045 (2009).

# Contents

| 1 | Introduction                                                                                                                                                                                                                                                       |                                               |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| 2 | Basics of field-effect transistors and integrated circuits         2.1 Metal-semiconductor junction         2.2 Metal-insulator-semiconductor junction         2.3 Operation principles of unipolar field-effect transistors         2.4 Integrated Logic Circuits | <b>5</b><br>9<br>15<br>19                     |  |

| 3 | Device fabrication and characterization3.1Pulsed-laser deposition3.2Direct-current sputtering3.3Photolithography3.4Current-voltage measurement3.5Capacitance-voltage measurement                                                                                   | <b>25</b><br>26<br>28<br>31<br>34             |  |

| 4 | Pulsed-laser deposited insulators and metal-insulator field-effect transistors         4.1 Metal-insulator-metal structures                                                                                                                                        | <b>37</b><br>38<br>43<br>49                   |  |

| 5 | ZnO-based metal-semiconductor field-effect transistors5.1Sapphire substrate5.2Glass substrate5.3Comparison of ZnO-MESFET with competing technologies                                                                                                               | <b>53</b><br>53<br>71<br>83                   |  |

| 6 | nverter5.1Simple Inverter5.2FET-logic Inverter5.3Schottky-diode FET-logic Inverter5.4Comparison with MESFET inverter devices from the literature                                                                                                                   | <b>87</b><br>87<br>93<br>97<br>100            |  |

| 7 | Transparent rectifying contacts         7.1       Preparation                                                                                                                                                                                                      | <b>103</b><br>103<br>105<br>105<br>108<br>108 |  |

#### Contents

| 8            | Summary and outlook                    | 111 |

|--------------|----------------------------------------|-----|

| Α            | Overview of photolithography templates | 115 |

| Bibliography |                                        | 121 |

| Lis          | st of own and contributed articles     | 131 |

| Sy           | mbols and Abbreviations                | 133 |

| Lis          | at of Figures                          | 137 |

| Lis          | st of Tables                           | 141 |

| Ac           | knowledgements                         | 142 |

# **1** Introduction

Transparent electronics (TE) have become an emerging field of material science and semiconductor physics in the past decade [Wag03]. It provides the vision of numerous applications and designs, such as transparent displays in the windshields of cars and planes, large-area displays in windows or as transparent flat-panel TVs. Furthermore, surfaces of products can be functionalized, e.g. realizing furniture or dishes with invisible electronics. And, using transparent displays, augmented-reality devices can be designed, which provide additional information to the seen objects, e.g. for aircraft mechanics, surgeons or tourists.

For that, transparent wide band gap materials, such as nitrides, carbides, diamond and oxides, with well-controlled electronic properties are necessary. From these materials, the group of oxides exhibit the highest variety of electronic properties. For oxides, the two extremes of the conductivity range are most developed and established in today's electronic industry. On the one hand, wide-bandgap ceramic oxides such as Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>/HfO<sub>2</sub>, and TiO<sub>2</sub> are introduced as highly insulating materials with high dielectric constants (high- $\kappa$ ) [Rob06] for the use in capacitors or as gate oxide in metal-insulator-semiconductor field-effect transistors (MISFET) replacing silicon oxide in micro-electronics. On the other hand, degenerately doped ( $n \sim 10^{21} \text{ cm}^{-3}$ ) oxides (transparent conducting oxides, TCO), foremost indium tin oxide (ITO) or Al-doped ZnO (AZO), are widely used as highly conductive transparent front contacts to various devices such as liquid-crystal displays, solar cells and touch screens [Min05]. Materials having intermediate conductivities with carrier concentrations in the range of  $10^{14}-10^{18} \text{ cm}^{-3}$  are referred to as transparent semiconducting oxides (TSO) [Gru10]. Their conductivity can be controlled via the manipulation of a depletion layer by a gate-electrode potential.

Using TSO, transparent field-effect transistors (TFET), necessary as pixel-driver for displays as well as for logic integrated circuits (IC) and memories, are developed as key active devices for TE. They are up to now mostly implemented as MISFET based on ZnO and related oxides.

However, such MISFET and related IC usually suffer from higher operating voltages due to the voltage drop across the insulator and limited switching speed due to carrier scattering at the interface between insulator and semiconductor. The channel mobility of MISFET is reduced compared to the bulk mobility of the semiconductor [Zeg04] resulting in lower gain. Due to the missing insulator and insulator/semiconductor interface, MESFET exhibit higher gain with lower operating voltages and the channel mobility equals the bulk mobility. They can further be fabricated more cost-efficiently.

The first completely transparent, i.e. substrate, channel, gate and contacts, TFET was fabricated by R. L. Hoffman *et al.* in 2003 [Hof03]. This MISFET comprises a ZnO channel, aluminium titanium oxide as gate dielectric and ITO as gate, source and drain contacts. Besides ZnO, which strongly tends to grow polycrystalline, the state of technology for MISFET also comprises amorphous-oxide channels, e.g. gallium indium zinc oxide or zinc tin oxide [Lee09b, Gö06], on glass substrates. Those devices exhibit channel mobilities in the range of 10 cm<sup>2</sup>/Vs and on/off-ratios > 10<sup>7</sup>.

Metal-semiconductor field-effect transistors (MESFET) are commonly known from GaAstechnology [Sed04] and are used for high-speed logic circuits due to their large channel mobility [Miz80, Tuy74]. For ZnO, MESFET technology was previously demonstrated by Ryu *et al.*, who used Ti as gate contact on *p*-type ZnO [Ryu05]. Kandasamy *et al.* used Pt-gate *n*-ZnO MESFET for hydrogen gas sensing [Kan07a]. Kao *et al.* used Pt/Au gate-contacts for their MESFET [Kao05]. However, the reported thin-film ZnO MESFET show inferior electronic properties with high gatevoltages between 4 and 20 V, very low on/off-ratios below 1 decade and barely obtained pinch-off and saturation behavior. On the basis of ZnO nanorods, MESFET and logic devices such as OR, AND, NOT, and NOR-gates have been realized by Park *et al.* using Au-gate contacts [Par05]. Their on/off ratio was ~  $10^4$  and a subthreshold slope between 100 and 200 mV/decade was achieved. Channel mobilities were neither reported for ZnO thin-film nor nanorod MESFET.

The goal of the present thesis is to realize and compare properties of ZnO thin-film-based FET (MIS-FET and MESFET) and to design, develop and investigate MESFET as an alternative approach to MISFET devices for the use in transparent circuitry. Design parameters shall be identified and the reliability of ZnO-MESFET is investigated.

This thesis is embedded in the German Research Foundation within the Collaborative Research Centre SFB 762: "Functionality of Oxide Interfaces". All investigated samples were fabricated and processed in the Semiconductor Physics Group at Universität Leipzig. Structural, morphologic, and electrical characterizations were also performed in this group.

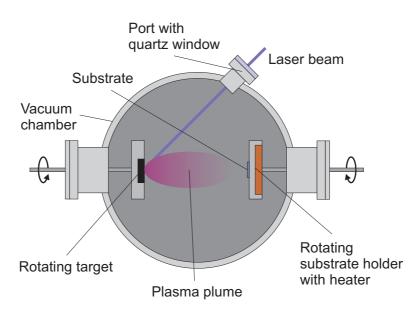

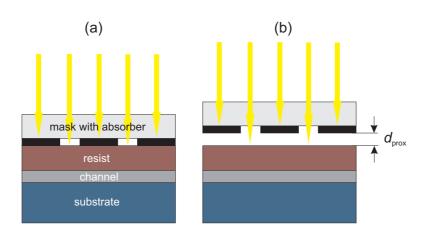

Preliminary to the fabrication of MESFET, PLD-grown high- $\kappa$  insulators and their application in MISFET are investigated in order to gain a basic understanding of the problems that are related to the insulator. For that, the conductive and capacitive properties of various insulators were studied in metal-insulator-metal (MIM) structures and the most promising dielectrics are then considered for metal-insulator-semiconductor (MIS) diodes on ZnO to electrically inquire the formation of defects at the insulator/semiconductor interface. Finally, MISFET were fabricated and analyzed.

MESFET were designed and fabricated on the basis of reactively dc-sputtered highly-rectifying Schottky contacts on ZnO [Laj09]. Based on a first-prinicples MESFET model [Sze81, Zeg04], physical parameters of MESFET such as channel thickness, doping and mobility as well as gate metals and contact design were varied and their influence on the performance of MESFET on sapphire substrate was investigated. The MESFET technology was then transferred to various low-cost glass substrates to prove their industrial applicability. For both kind of substrates, reliability tests were performed considering the degradation under bias stress, exposure to visible light and long-time stability. The properties of the MESFET were compared to MISFET within this work and and other reported MIS-FET.

Emanating from the findings on MESFET, three types of inverter circuits and a NOR-gate were realized. Their electrical performance as well as deviations from the ideal case were investigated.

Finally, a layer structure and preparation method for transparent rectifying contacts (TRC) wass developed. The TRC serve as basis of fully-transparent Schottky-diodes, MESFET and inverters for applications in transparent electronics. Transparent MESFET and inverters were compared to other reported transparent devices and the opaque devices presented in this work.

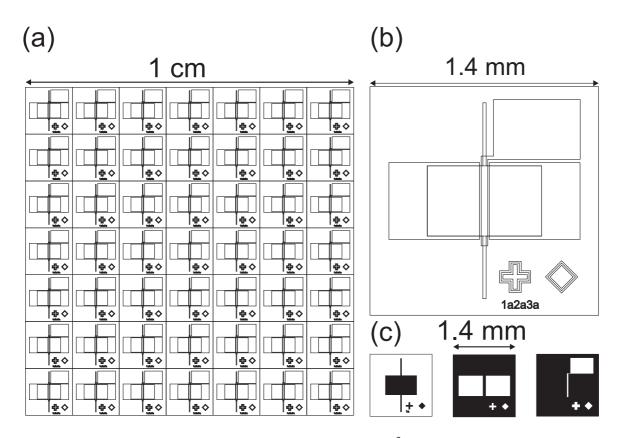

The pulsed-laser deposition (PLD) of the samples was carried out by Dipl.-Ing. H. Hochmuth, photolithography and processing was done in collaboration with Dipl.-Ing. G. Biehne and M. Hahn, dc-sputtering of the contact metalls was performed in collaboration with H. Münch. The precharacterization of the FET samples with spectroscopic ellipsometry was done by the Ellipsometry Workgroup (Dipl.-Phys. C. Sturm, Dipl.-Phys. H. Hilmer, Dr. R. Schmidt-Grund, *et al.*), Halleffect measurements were performed by Dipl.-Phys. M. Brandt, Dipl.-Phys. R. Heinhold and Dipl.-Phys. T. Lüder. SEM cross-sections and EDX-analysis were carried out by Dipl.-Phys. J. Lenzner, TEM was performed by Dr. G. Wagner. XRD and AFM was measured by Dipl.-Phys. M. Lorenz, AFM was also measured by Dipl.-Phys. M. Brandt and Dipl.-Phys. G. Zimmermann. Electrical measurements on MESFET on glass substrates, inverters and MIM/MIS-capacitors were performed in collaboration with Dipl.-Phys. M. Lorenz, Dipl.-Phys. F. Schein and M.Sc. N. Yensuong, respectively, within the scope of their diploma and master thesises. The electrical characterization of transparent devices was done in collaboration with Dipl.-Phys. A. Lajn and T. Diez. Chemical analysis by means of TOF-SIMS measurements was performed by S. Richter (Fraunhofer CSP, Halle).

# 2 Basics of field-effect transistors and integrated circuits

Field-effect transistors are unipolar transistors where only one type of charge carriers (either electrons or holes) are involved in the current transport. This thesis mainly focuses on MESFET and MIS-FET whose gate structure is a metal-semiconductor junction (Schottky diode) or a metal-insulator-semiconductor junction (MIS diode), respectively. The physical basics of these structures shall be the topic of this chapter. At the end of this chapter, the basics of integrated logic circuits, that were realized within this work, will be presented.

# 2.1 Metal-semiconductor junction

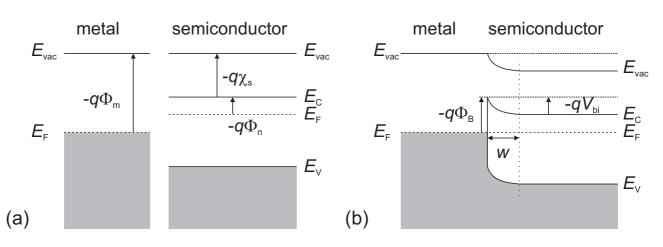

First metal-semiconductor junctions on ZnO were investigated by C. A. Mead in 1965 [Mea65]. The formation of such a junction on any *n*-type semiconductors can be described by the model developed in 1939 by W. Schottky [Sch39] and N. F. Mott [Mot39]. It is therefore called Schottky-Mott diode or Schottky contact. The rectifying partially oxidized gate contacts within this thesis can be well treated by this model. It will be shown in Cha. 5, that metall-oxide Schottky contacts on ZnO thin films exhibit a higher barrier height than pure metallic Schottky contacts.

## 2.1.1 Band diagram

Within the Schottky-Mott model, a Schottky contact is obtained in the case:

$$\phi_{\rm m} > \chi_{\rm s} + \phi_{\rm n} , \qquad (2.1)$$

where  $\phi_{\rm m}$  is the metal's work function,  $\chi_{\rm s}$  is the electron affinity of the semiconductor and  $\phi_{\rm n} = E_{\rm C} - E_{\rm F}$  is the energy difference between conduction band edge  $E_{\rm C}$  and Fermi energy level  $E_{\rm F}$ . The formation of a Schottky contact is illustrated in the band diagram of Fig. 2.1. When both materials are brought in ideal contact and surface states and interface roughness are neglected, electrons from the semiconductor will move to the energetically more favorable states in the metal. A current flows until the Fermi levels of both sides are equal. The electrons were provided by donors in the semiconductor, whose positively charged cores form a space charge region in the vicinity of the metal-semiconductor interface. A potential barrier  $\phi_{\rm B}$  is formed due to charge neutrality and the subsequent band bending in the semiconductor. The Schottky barrier height is given by [Sze81]:

$$\phi_{\rm B} = \phi_{\rm m} + \chi_{\rm s} \ . \tag{2.2}$$

**Figure 2.1:** Band diagrams of a Schottky metal and a *n*-type semiconductor a) before contact and b) after formation of the Schottky contact.

**Table 2.1:** Work function  $\phi_m$  and Schottky barrier height  $\phi_B$  for various pure metals assuming an electron affinity for ZnO of  $\chi_s = 4.1$  eV [Nak07, Jac84].

|    | $q\phi_{ m m}$ | $q\phi_{ m B}$ |

|----|----------------|----------------|

|    | (eV)           | (eV)           |

| Pt | 5.65           | 1.55           |

| Pd | 5.12           | 1.02           |

| Au | 5.10           | 1.10           |

| Ag | 4.26           | 0.16           |

It is in first principles independent of the doping or applied external voltages. In the semiconductor, the built-in voltage  $V_{bi} = \phi_m - (\chi_s + \phi_n)$  drops over the width w of the space charge region. A space charge region is also formed in the metal. However, due to the very high electron density and screening effects, it is only a few angstroms wide. Table 2.1 lists the work function and Schottky barrier height on ZnO for the pure metals, that were reactively sputtered in this work. Note, that Ag/ZnO would result in very low Schottky barrier height and would lead to an ohmic contact. Ag<sub>x</sub>O, however, leads to much higher  $\phi_B$  as will be shown in Sec. 5.1. The electron affinity of ZnO is thereby assumed to be  $\chi_s = 4.1$  eV [Nak07]. However, Jacobi *et al.* showed, that  $\chi_s$  is higher for the oxygen terminated surface than for the zinc terminated surface [Jac84]. Since, for the very thin ZnO films used as channel in this thesis, the surface termination is not clear, the average  $\chi_s$  of both surfaces (4.1 eV) is assumed.

#### 2.1.2 Capacitance-voltage characteristic

The space charge region underneath a Schottky contact can be considered as a plate capacitor with the capacitance per unit area

$$C = \frac{\epsilon_{\rm r}\epsilon_0}{w} = \frac{Q}{V} , \qquad (2.3)$$

where  $\epsilon_r$  and  $\epsilon_0$  are the dielectric constant of the semiconductor and the vacuum dielectric constant, respectively. Q is the charge that was measured at a given voltage V. The space charge region width w can be determined making the assumption that the space charge is given by the net doping concentration:  $\rho = q(N_D - N_A)$ . Within the Schottky approximation, no charge and no electric field shall be outside of the space charge region, i.e.  $\rho = 0$  and  $\mathcal{E} = \frac{\partial V}{\partial x} = 0$ . Then, the one dimensional Poisson equation

$$\Delta_x V = -\frac{\rho}{\epsilon_r \epsilon_0} \tag{2.4}$$

can be solved with the ansatz  $V = V_0 + V_1 x + V_2 x^2$  and the boundary condition  $V(0) = -V_{bi}$ . Double integration results in the potential:

$$V(x) = -V_{\rm bi} + \frac{q(N_{\rm D} - N_{\rm A})}{\epsilon_{\rm r}\epsilon_0} \left(wx - \frac{1}{2}x^2\right) \,. \tag{2.5}$$

Due to the finite width of the space charge region (V(w) = 0), w can be extrated from Eqn. 2.5:

$$w = \sqrt{\frac{2\epsilon_{\rm r}\epsilon_0}{q(N_{\rm D} - N_{\rm A})}} V_{\rm bi} . \tag{2.6}$$

Applying a positive external voltage  $V_{\text{ext}}$  and considering the thermal energetic broadening of electrons  $k_{\text{B}}T/q$  reduces w:

$$w = \sqrt{\frac{2\epsilon_{\rm r}\epsilon_0}{q(N_{\rm D} - N_{\rm A})}} \left( V_{\rm bi} - V_{\rm ext} - \frac{k_{\rm B}T}{q} \right).$$

(2.7)

From Eqns. 2.3 and 2.7, the net doping concentration can be calculated from the slope of  $C^{-2}(V)$ :

$$N_{\rm D} - N_{\rm A} = -\frac{2}{q\epsilon_{\rm r}\epsilon_0} \left(\frac{\partial C^{-2}}{\partial V}\right)^{-1} \,. \tag{2.8}$$

Within this work, the determination of the net doping concentration is done by means of quasi-static capacitance-voltage measurements as described in Sec. 3.5.

#### 2.1.3 Current-voltage characteristic

The principle conduction mechanisms for *n*-type Schottky diodes are:

- 1. Thermionic emission of electrons above the barrier.

- 2. Tunneling of electrons through a thin barrier; e.g. for highly doped semiconductors.

- 3. Recombination within the space charge region.

4. Injection of holes from the metal and subsequent recombination outside of the space charge region.

For moderately doped semiconductors, thermionic emission is the predominant mechanism. The Schottky-diode characteristics within this thesis are treated by thermionic emission theory. Its derivation is based on the descriptions in [Sze81] and [Gru06].

The emission of electrons from the semiconductor to the metal above the barrier is given by

$$j_{\rm sm} = -\int q v_{\rm x} dn , \qquad (2.9)$$

where dn is the electron density in a small energy interval given by the density of states D(E) and the Fermi distribution f(E). For a bulk semiconductor and using the Boltzmann approximation, dn is:

$$dn = D(E)f(E)dE = \frac{4\pi (2m^*)^{3/2}}{h^3} \sqrt{E - E_{\rm C}} \cdot \exp\left(\frac{E - E_{\rm F}}{k_{\rm B}T}\right) dE .$$

(2.10)

Using the substitutions

$$E - E_{\rm C} = \frac{m^*}{2} v^2 \tag{2.11}$$

$$dE = m^* v dv = 4\pi v^2 dv_x dv_y dv_z$$

(2.12)

$$E - E_{\rm F} = E - E_{\rm C} + q(\phi_{\rm B} + V_{\rm bi}),$$

(2.13)

Eqn. 2.10 can be re-written as:

$$dn = 2\left(\frac{m^*}{h}\right)^3 \exp\left(\frac{q(\phi_{\rm B} + V_{\rm bi})}{k_{\rm B}T}\right) \exp\left(\frac{\frac{m^*}{2}v^2}{k_{\rm B}T}\right) dv_{\rm x} dv_{\rm y} dv_{\rm z} .$$

(2.14)

With that, the integral in Eqn. 2.9 can be solved and the current density results in

$$j_{\rm sm} = A^* T^2 \exp\left(\frac{q\phi_{\rm B}}{k_{\rm B}T}\right) \exp\left(\frac{qV}{k_{\rm B}T}\right) \,, \tag{2.15}$$

where V is the external applied voltage and  $A^* = \frac{4\pi q m^* k_B^2}{h^3}$  is the Richardson constant, which is  $A^* = 32.4 \frac{A}{cm^2 K^2}$  for ZnO.

With zero net current for V = 0 in thermal equilibrium, the current from the metal to the semiconductor can be extracted from Eqn. 2.15:

$$j_{\rm ms} = -A^* T^2 \exp\left(\frac{q\phi_{\rm B}}{k_{\rm B}T}\right) \,. \tag{2.16}$$

Thus, the current-voltage characteristic of the Schottky diode is given by

$$j = \underbrace{A^* T^2 \exp\left(\frac{q\phi_{\rm B}}{k_{\rm B}T}\right)}_{j_{\rm S}} \left[\exp\left(\frac{qV}{k_{\rm B}T}\right) - 1\right], \qquad (2.17)$$

with  $j_s$  being the saturation current density. If the Schottky effect, i.e. the change of barrier height with bias voltage, is considered, the ideality factor

$$\eta = 1 + \frac{\partial \phi_{\rm B}}{\partial V} \tag{2.18}$$

has to be introduced. The ideality factor should be close to unity  $\eta \le 1.03$  if the voltage dependence of the barrier height is only due to image force lowering. However, the real values are higher, which is most probably due to an inhomogeneous barrier height [Wer91].

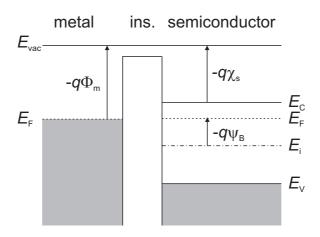

# 2.2 Metal-insulator-semiconductor junction

#### 2.2.1 Band diagram

In this section, the ideal MIS diode is considered, i.e. under an applied external voltage, charges only exist either at the metal-insulator interface or, with opposing charges, in the semiconductor — no charges are allowed within the insulator. The case of a non-ideal insulator is discussed in Sec. 3.4.2. The insulator is ideal, when its resistivity is infinite. It also implies the absence of charges at the insulator-semiconductor interface (the opposite case is discussed in Sec. 3.5). At zero external voltage, there is no difference between the metal's and the semiconductor's work functions:

$$\phi_{\rm ms} = \phi_{\rm m} - \phi_{\rm s} = \phi_{\rm m} - \left(\chi_{\rm s} + \frac{E_{\rm g}}{2q} - \psi_{\rm B}\right) = 0 , \qquad (2.19)$$

where  $\phi_{\rm m}$  and  $\phi_{\rm s}$  are the work functions of the metal and the semiconductor, respectively,  $\chi_{\rm s}$  is the electron affinity of the semiconductor,  $E_{\rm g}$  the band gap, q the elementary charge and  $\psi_{\rm B}$  the difference between Fermi energy level  $E_{\rm F}$  and the intrinsic energy level  $E_{\rm i}$ . The definitions of the potentials are shown within the band diagram (Fig. 2.2) of an ideal MIS diode for flat-band condition (Eqn. 2.19).

For *n*-type semiconductors,  $\psi_{\rm B}$  can be obtained from the bulk electron concentration

$$n \approx N_{\rm D} = n_{\rm i} e^{(E_{\rm i} - E_{\rm F})/k_{\rm B}T} , \qquad (2.20)$$

where  $n_i$  is the intrinsic carrier concentration,  $N_D$  the donor concentration. Therefore,  $\psi_B$  can be obtained as

$$\psi_{\rm B} = \frac{k_{\rm B}T}{q} \ln \frac{N_{\rm D}}{n_{\rm i}} \,. \tag{2.21}$$

Figure 2.2: Band diagram of an ideal MIS diode in flat-band condition (no external voltage applied).

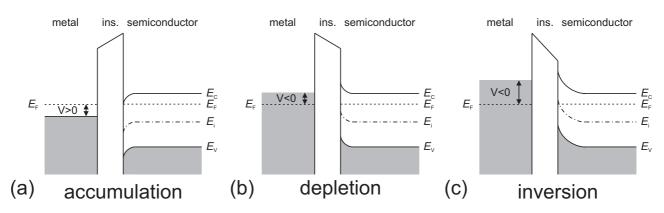

**Figure 2.3:** Band diagrams of an ideal MIS-diode with applied external voltage: a) accumulation (V > 0), b) depletion (V < 0) and c) inversion ( $V \ll 0$ ).

When an external voltage is applied to the MIS structure, three cases are possible (Fig. 2.3): a) accumulation, b) depletion and c) inversion. To explain these cases, the potential  $\psi$  is defined as the difference between the intrinsic energy level in the bulk of the semiconductor and at a given position *x*:

$$\psi(x) = -\frac{E_{\rm i}(x) - E_{\rm i}(\infty)}{q} \,. \tag{2.22}$$

The potential is zero in the bulk and defined as surface potential  $\psi_s$  for x = 0.

#### a) Accumulation

If the applied voltage is positive on the metal side of the junction, the bands are bent downward with respect to the Fermi energy level, as no current flow is allowed through the ideal insulator (Fig. 2.3a). The surface potential  $\psi_s$  is positive. Due to charge neutrality, the positive charges at the metal gate are equalized by an accumulation of electrons at the semiconductor surface ("field-effect").

#### b) Depletion

The band is bent upwards as negative voltage is applied at the metal. The surface potential  $\psi_s$  is now negative but does not exceed  $\psi_B$ , i.e.  $E_i$  does not cross  $E_F$ . A depletion layer is formed, similar to the case of a Schottky contact, which expands as the voltage is increased in the negative direction.

#### **C) Inversion**

When the negative voltage is further increased above  $\psi_B$ ,  $E_i$  crosses  $E_F$ . Thermal generation of holes becomes more and more probable. The hole density at the surface is then larger than the electron density. An inversion layer is formed at the surface. For ZnO, inversion due to thermal generation of holes cannot be observed because of the large band gap as discussed in Sec 2.2.2.

#### 2.2.2 Capacitance-voltage characteristic

In order to derive a model for the capacitance-voltage (CV) characteristic of a MIS diode, a relationship between the surface charge  $Q_s$ , surface electric field  $\mathcal{E}_s$  and surface potential  $\psi_s$  is required. The following derivation is based on [Sze81] for an *n*-type semiconductor.

The relation between the potential  $\psi$  and the densities of holes and electrons in the semiconductor is given by

$$n_{\rm n}(x) = n_{\rm n_0} \exp\left(\frac{q\psi(x)}{k_{\rm B}T}\right), \qquad (2.23)$$

$$p_{\rm n}(x) = p_{\rm n_0} \exp\left(\frac{-q\psi(x)}{k_{\rm B}T}\right), \qquad (2.24)$$

where  $n_{n_0}$  and  $p_{n_0}$  are the densities of electrons and holes at equilibrium, respectively. Therefore, the surface density for electrons and holes at x = 0 can be obtained for  $\psi(0) = \psi_s$ :

$$n_{\rm s} = n_{\rm n_0} \exp\left(\frac{q\psi_{\rm s}}{k_{\rm B}T}\right), \qquad (2.25)$$

$$p_{\rm s} = p_{\rm n_0} \exp\left(\frac{-q\psi_{\rm s}}{k_{\rm B}T}\right) \,. \tag{2.26}$$

In order to obtain the function  $\psi(x)$ , the one dimensional Poisson equation (Eqn. 2.4) has to be solved with the total space charge

$$\rho(x) = q(N_{\rm D} - N_{\rm A} + p_{\rm n}(x) - n_{\rm n}(x)) .$$

(2.27)

Since far from the surface, charge neutrality has to be considered with  $\psi(\infty) = 0$  and  $\rho(x) = 0$ , it can be seen that  $n_{n_0} - p_{n_0} = N_D - N_A$ . With the thermal potential  $\phi_t = k_B T/q$  and the permittivity of the semiconductor  $\epsilon_s = \epsilon_r \epsilon_0$ , the Poisson equation can be written as

$$\frac{\partial^2 \psi}{\partial x^2} = -\frac{q}{\epsilon_{\rm s}} \left[ p_{\rm n_0} \left( \exp\left(-\frac{\psi(x)}{\phi_{\rm t}}\right) - 1 \right) - n_{\rm n_0} \left( \exp\left(\frac{\psi(x)}{\phi_{\rm t}}\right) - 1 \right) \right] \,. \tag{2.28}$$

This equation is then multiplied from both sides with  $2(\partial \psi/\partial x)$  such that the left side becomes  $(\partial/\partial x)(\partial \psi/\partial x)^2$ . Integration from the bulk toward the surface with  $\mathcal{E} = -\partial \psi/\partial x$  being the electric field leads to

$$\mathcal{E} = \pm \frac{\sqrt{2}\phi_{\rm t}}{L_{\rm D}} \mathcal{F}(\psi) \;. \tag{2.29}$$

For  $\psi > 0$ , the sign is negative and for  $\psi < 0$  it is positive. The notation of  $\mathcal{F}(\psi)$  and the extrinsic Debye length  $L_{\rm D}$ , with  $\frac{p_{\rm n_0}}{n_{\rm n_0}} = \frac{n_{\rm i}^2}{N_{\rm D}^2}$ , is:

$$\mathcal{F}(\psi) = \left[\frac{n_{i}^{2}}{N_{D}^{2}}\left(\exp\left(-\frac{\psi}{\phi_{t}}\right) + \frac{\psi}{\phi_{t}} - 1\right) + \left(\exp\left(\frac{\psi}{\phi_{t}}\right) - \frac{\psi}{\phi_{t}} - 1\right)\right], \qquad (2.30)$$

$$L_{\rm D} = \sqrt{\frac{\epsilon_{\rm s}\phi_{\rm t}}{qN_{\rm D}}} \,. \tag{2.31}$$

From Eqn. 2.29, the surface field is given by  $\mathcal{E}_s = \pm \frac{\sqrt{2}\phi_t}{L_D} \mathcal{F}(\psi_s)$  and the surface charge per unit area can be obtained by Gauss law

$$Q_{\rm s} = -\epsilon_{\rm s} \mathcal{E}_{\rm s} = \mp \frac{\sqrt{2}\epsilon_{\rm s}\phi_{\rm t}}{L_{\rm D}} \mathcal{F}(\psi_{\rm s}) .$$

(2.32)

This equation is valid for all  $\psi_s$ , i.e. for accumulation, depletion and inversion. The capacitance of the depletion layer can be derived using Eqn. 2.32:

$$C_{\rm D} = \frac{\partial Q_{\rm s}}{\partial \psi_{\rm s}} = -\frac{\epsilon_{\rm s}}{\sqrt{2}L_{\rm D}} \frac{\frac{n_{\rm i}^2}{N_{\rm D}^2} \left(1 - e^{-\frac{\psi_{\rm s}}{\phi_{\rm t}}}\right) + e^{\frac{\psi_{\rm s}}{\phi_{\rm t}}} - 1}{\mathcal{F}(\psi_{\rm s})} .$$

$$(2.33)$$

By means of series expansion of the exponential terms of Eqn. 2.33, the capacitance of the depletion layer at flat-band condition  $\psi_s = 0$  can be obtained as

$$C_{\rm D}(\psi_{\rm s}=0) = \frac{\epsilon_{\rm s}}{L_{\rm D}} . \tag{2.34}$$

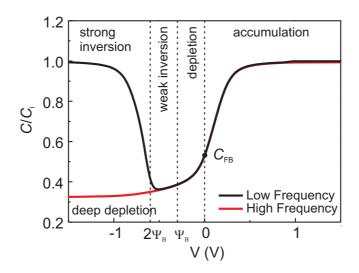

Figure 2.4: Ideal CV characteristic of a ZnO MIS diode for high and low measurement frequencies.

An applied external voltage V will partially drop across the insulator and the semiconductor:

$$V = V_{\rm i} + \psi_{\rm s} , \qquad (2.35)$$

where

$$V_{\rm i} = \frac{|Q_{\rm s}|}{C_{\rm i}} = \frac{|Q_{\rm s}|d}{\epsilon_{\rm i}}$$

(2.36)

is the voltage drop across the insulator and  $C_i$  is the insulator capacitance per unit area with  $\epsilon_i = \kappa \epsilon_0$  being the insulator permittivity and  $\kappa$  being the dielectric constant of the insulator.

A change of the applied voltage V will also effect  $V_i$  and  $\psi_s$  to equalize the system. Charge neutrality has to be considered:

$$Q_{\rm m} = -(Q_{\rm p} + Q_{\rm D}) , \qquad (2.37)$$

where  $Q_{\rm m}$  is the charge at the metal gate,  $Q_{\rm p}$  is the charge in the inversion layer and  $Q_{\rm D} = qwN_{\rm D}$  is the depletion layer charge.

The total capacitance of the MIS diode can now be determined considering it as a capacitor with a dielectric in series to the depletion layer and combining Eqns. 2.33, 2.35 and 2.36:

$$C = \frac{1}{\frac{1}{C_{\rm i}} + \frac{1}{C_{\rm D}}} \,. \tag{2.38}$$

The ideal CV characteristic for a ZnO MIS diode obtained from Eqn. 2.38 is shown in Fig. 2.4.

In accumulation (V > 0), the total capacitance is close to the insulator capacitance due to screening of the charges in the semiconductor by accumulated electrons at the insulator-semiconductor interface. The capacitance at flat-band condition is obtained from Eqns. 2.34 and 2.38:

$$C_{\rm FB} = \left(\frac{d}{\epsilon_{\rm i}} + \frac{L_{\rm D}}{\epsilon_{\rm s}}\right)^{-1} \,. \tag{2.39}$$

For voltages smaller than the flat-band voltage  $V_{\rm FB}$ , the depletion region is formed and, according to Eqn. 2.38, the total capacitance decreases. The depletion region can be analyzed analogous to the Schottky diode (Sec. 2.1.2); the net doping concentration can be obtained from Eqn. 2.8.

The ideal CV characteristic (Fig. 2.4) passes a minimum and then increases in the inversion regime. However, this depends on the measurement frequency. At low frequency, the generation rate of minority carriers can follow the voltage signal. As a large voltage is applied, the strong inversion regime occurs and from Eqn. 2.21 the surface potential is then [Tsi03]:

$$\psi_{\rm s}^{\rm inv} \simeq 2\psi_{\rm B} = 2\phi_{\rm t} \ln \frac{N_{\rm D}}{n_{\rm i}} , \qquad (2.40)$$

where the hole density becomes equal to the majority carrier concentration. The inversion layer screens the semiconductor from the electric field and the total capacitance C equals the insulator capacitance  $C_i$  again.

For high frequency, the MIS capacitance does not increase again. This case is called deep depletion (cf. Fig. 2.4). The variation in the voltage signal is too fast to modulate the minority carrier density.

In large band gap semiconductors such as GaN [Has00] and ZnO, the inversion case of the MIS CV measurement can not be easily observed. It can be shown from [Zeg04], that the minimum rate of time required for inversion can be approximated by the ratio of the total charge of the inversion layer  $|Q_p|$  and the generation rate *G* of minority carriers. Simplifying the case to only consider generation in the neutral region, the required time and voltage change per time is given by:

$$t = \frac{Q_{\rm p}}{qGL_{\rm n}}\frac{dV}{dt} < \frac{qGL_{\rm n}}{C_{\rm i}} = \frac{qn_{\rm i}}{2C_{\rm i}}\sqrt{\frac{\mu_{\rm n}\phi_{\rm t}}{\tau_{\rm n}}},\tag{2.41}$$

where  $\tau_n$  is the carrier lifetime,  $L_n$  is the diffusion length and  $\mu_n$  is the electron mobility. For ZnO, it can be estimated with typical values of  $\tau_n \sim 1 \mu s$ , dV = 0.1 V,  $C_i \sim 1 \times 10^{-7} \text{ F/cm}^2$ ,  $\mu_n \sim 50 \text{ cm}^2/\text{Vs}$  and  $n_i \sim 10^0 \text{ cm}^{-3}$  [Man06, Pea04]. The approximate minimum measurement time for one data point in CV measurements to see inversion in ZnO would be

$$dt > 10^8 \,\mathrm{s}$$

. (2.42)

Thus, it is hard to observe inversion in ZnO MIS diodes in thermal equilibrium.

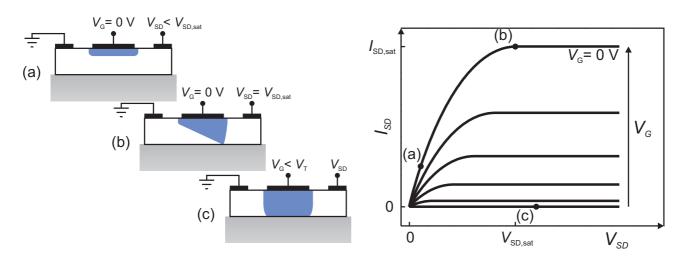

Figure 2.5: General principle and schematic output characteristic of a MESFET.

# 2.3 Operation principles of unipolar field-effect transistors

#### 2.3.1 Metal-semiconductor field-effect transistors

#### **Operation principle**

On behalf of using ZnO as channel material, the general principle (Fig. 2.5) of a *n*-type, normally-on MESFET shall be considered in this section. For a gate voltage  $V_{\rm G} = 0$  V and a source-drain voltage of  $V_{\rm SD} = 0$  V, the transistor is in thermodynamic equilibrium; no currents occur. By increasing  $V_{\rm SD} > 0$ , a source-drain current  $I_{\rm SD}$  will flow due to the electric field between source and drain. Initially, for low  $V_{\rm SD}$ , the channel resistance is constant and  $I_{\rm SD}$  depends linearly on  $V_{\rm SD}$  according to Ohm's law (cf. Fig. 2.5a). With increasing  $V_{\rm SD}$ , the voltage drop across the channel and the corresponding potential difference leads to an expansion of the depletion layer at the drain side of the channel, which is larger at the drain side of the channel. At a certain voltage, called saturation voltage  $V_{\rm SD,sat}$ , the depletion layer width equals the channel thickness, i.e. the channel is pinched off (Fig. 2.5b). A further increase of  $V_{\rm SD}$  to  $V_{\rm SD,sat} + \Delta V$  shifts the pinch-off point towards the source contact and  $\Delta V$  drops across the laterally expanded depletion layer. The voltage drop in the remaining open channel (from source to the pinch-off point) remains therefore constant at  $V_{\rm SD,sat}$ . Thus, according to Kirchoff's law, the diffusive source-drain current saturates ( $I_{\rm SD}(V_{\rm SD} > V_{\rm SD,sat}) = I_{\rm SD,sat}$ ). An excessive increase of  $V_{\rm SD}$  results in the breakdown of the channel. Impact ionization leads to increased generation of electron-hole pairs and  $I_{\rm SD}$  will uncontrollably increase.

The cross-section of the conducting channel can also be controlled by varying the gate voltage  $V_G$ . The width of the depletion region under the Schottky gate-contact can be expanded according to Eqn. 2.7, such that the complete channel is depleted and  $I_{SD} = 0$  for all applied  $V_{SD}$  (Fig. 2.5c). The gate voltage needed to completely close the channel is called turn-on voltage  $V_T$ . With increasing negative  $V_G$  and constant  $V_{SD}$ , the ohmic resistance in the linear regime of the output characteristic increases due to the decreasing cross-section of the conducting channel. The pinch-off at the drain contact is then already reached for smaller  $V_{SD}$ , i.e.  $V_{SD,sat} \rightarrow 0$  for  $V_G \rightarrow V_T$ . This implies, that a decreasing

part of the constant  $V_{SD}$  drops over the non-depleted part of the channel and  $I_{SD}$  is decreasing until, finally,  $V_{SD,sat} = 0$  and  $I_{SD} = 0$  in the ideal case.

#### **Current-voltage characteristic**

For the derivation of the current-voltage characteristic of a MESFET, the following assumptions are made:

- 1. The lateral direction, parallel to the substrate is referred to a x-direction.

- 2. The channel is homogeneously doped with a doping concentration  $N_{\rm D}$ .

- 3. The size of the depletion layer is slowly changing in *x*-direction ( $\mathcal{E}_x \ll \mathcal{E}_y$ , "gradual channel approximation").

- 4. The length of the gate is larger than the channel thickness ( $L \gg d$ , "long-channel approximation").

- 5. The mobility of the electrons is constant ( $v = \mu \mathcal{E}_x$ ).

- 6. The current over the gate is negligible.

The drift current density is given by the mobile charges in the channel  $(n = N_D)$  and their velocity:

$$j(x) = Qv(x) = -qN_{\rm D}\mu\mathcal{E}_{\rm x} = qN_{\rm D}\mu\frac{\partial V}{\partial x}.$$

(2.43)

Therefore, the source-drain current in the neutral part of the channel with cross-section A = W(d - w(x)), W being the channel width and  $w(x) = \sqrt{\frac{2\epsilon_{\rm r}\epsilon_0}{eN_{\rm D}}}(V_{\rm bi} + V_{\rm G} + V(x))$  being the depletion layer depth according to Eqn. 2.7, is given by

$$I_{\rm SD}(x) = j(x)A = qN_{\rm D}\mu \frac{dV}{dx}(d - w(x))W.$$

(2.44)

$I_{\rm SD}$  is constant along the channel due to Kirchhoff's second law; i.e. with  $\int_0^L I_{\rm SD}(x) dx = L I_{\rm SD}$ :

$$I_{\rm SD} = \frac{qN_{\rm D}\mu W}{L} \int_0^L \frac{dV}{dx} (d - w(x)) dx$$

(2.45)

$$= \frac{qN_{\rm D}\mu W}{L} \int_0^{V_{\rm SD}} \left( d - \sqrt{\frac{2\epsilon_{\rm r}\epsilon_0}{qN_{\rm D}}} (V_{\rm bi} + V_{\rm G} + V) \right) dV.$$

(2.46)

The solution of this integral can be written as [Sze81, Zeg04]:

$$I_{\rm SD} = g_{\rm max} \left( V_{\rm SD} - \frac{2}{3\sqrt{V_{\rm P}}} \left[ (V_{\rm bi} + V_{\rm SD} + V_{\rm G})^{3/2} - (V_{\rm bi} + V_{\rm G})^{3/2} \right] \right) \,, \tag{2.47}$$

where

$$g_{\max} = \frac{q\mu N_{\rm D} dW}{L} \tag{2.48}$$

is the maximum transconductance of the channel obtained for w = 0 and

$$V_{\rm P} = \frac{q N_{\rm D} d^2}{2\epsilon_{\rm r} \epsilon_0} \tag{2.49}$$

being the pinch-off voltage obtained for w = d.

Eqn. 2.47 is valid as long as the width of the undepleted channel d - w(x) is positive, i.e. for

$$V_{\rm SD} \le V_{\rm G} - V_{\rm T}$$

, (2.50)

where  $V_{\rm T} = V_{\rm bi} - V_{\rm P}$  is the threshold voltage of the MESFET. For small  $V_{\rm SD}$ , Eqn. 2.47 can be linearized to

$$I_{\rm SD} = g_{\rm max} \left( 1 - \sqrt{\frac{V_{\rm bi} + V_{\rm G}}{V_{\rm P}}} \right) V_{\rm SD} \propto V_{\rm SD} .$$

$$(2.51)$$

With further increasing  $V_{SD}$ ,  $I_{SD}$  saturates. Inserting the saturation voltage  $V_{SD,sat} = V_G - V_T$  into Eqn. 2.47 leads to the saturation current

$$I_{\rm SD,sat} = g_{\rm max} \left( V_{\rm G} - V_{\rm T} - \frac{2}{3} \left( V_{\rm P} - \frac{(V_{\rm bi} - V_{\rm G})^{3/2}}{\sqrt{V_{\rm P}}} \right) \right) \,.$$

(2.52)

The MESFET channel mobility can now be determined either from the output characteristic  $I_{SD}(V_{SD})$  for  $V_{SD} \rightarrow 0$  using the drain transconductance  $g_{D0}$  or from the transfer characteristic in the saturation regime  $I_{SD,sat}(V_G)$  using the saturation forward transconductance  $g_{m,sat}$ . The relation between both values is

$$g_{\rm D0} = \frac{\partial I_{\rm SD}}{\partial V_{\rm SD}} \bigg|_{V_{\rm SD} \to 0} = g_{\rm max} \left[ 1 - \left( \frac{V_{\rm bi} + V_{\rm G}}{V_{\rm P}} \right)^{1/2} \right] = \frac{\partial I_{\rm SD,sat}}{\partial V_{\rm G}} = g_{\rm m,sat} .$$

$$(2.53)$$

From Eqn. 2.53,  $g_{\text{max}}$  can be extracted and inserted in Eqn. 2.48. The channel mobility is then given by

$$\mu_{\rm ch} = \frac{g_{\rm max}}{qN_{\rm D}d(W/L)} \ . \tag{2.54}$$

#### 2.3.2 Metal-insulator-semiconductor field-effect transistors

As described in Sec. 2.2.2, inversion cannot be achieved for ZnO MISFET in thermodynamic equilibrium. For this reason, a MISFET model is considered, where no inversion charge occurs. Instead in an electrostatic approach, the induced charge  $Q_{ind}$  within the channel of the transistor is given by the insulator capacitance  $C_i$  and the difference between applied gate voltage and turn-on voltage  $V_G - V_T$ :

$$Q_{\rm ind} = -C_{\rm i}(V_{\rm G} - V_{\rm T}),$$

(2.55)

assuming that the charge density is constant along the channel. The source-drain current according to Eqn. 2.43 is then given by

$$I_{\rm SD} = -Q_{\rm ind}\nu W = -Q_{\rm ind}\mu \frac{W}{L} \cdot V_{\rm SD} , \qquad (2.56)$$

where  $v = \mu \mathcal{E} = \mu \frac{V_{SD}}{L}$  is the charge carrier's velocity. Inserting Eqn. 2.55 into Eqn. 2.56 leads to

$$I_{\rm SD} = \mu C_{\rm i} \frac{W}{L} (V_{\rm G} - V_{\rm T}) V_{\rm SD} .$$

(2.57)

This is the linear model of the MISFET [Zeg04], which is valid for small  $V_{SD}$ , where the transistor acts like a linear resistor whose resistance is modulated by  $V_{G}$ .

Taking into account that the electric field varies along the channel from source to drain, as it does for the MESFET, a small section dx and a local channel voltage  $V_{\rm C}$  is considered. The linear model (Eqn. 2.57) still applies for this section, yielding:

$$I_{\rm SD} = \mu C_{\rm i} \frac{W}{dx} (V_{\rm G} - V_{\rm C} - V_{\rm T}) dV_{\rm C} .$$

(2.58)

Both sides can be integrated from source to drain, again with  $I_{SD}$  being constant due to Kirchhoff's second law.

$$\int_{0}^{L} I_{\rm SD} dx = \mu C_{\rm i} W \int_{0}^{V_{\rm SD}} (V_{\rm G} - V_{\rm C} - V_{\rm T}) dV_{\rm C}$$

(2.59)

The integration results in:

$$I_{\rm SD} = \mu C_{\rm i} \frac{W}{L} \left[ (V_{\rm G} - V_{\rm T}) V_{\rm SD} - \frac{V_{\rm SD}^2}{2} \right] \,.$$

(2.60)

$I_{SD}$  first increases linearly with  $V_{SD}$  before it reaches a maximum value and saturates due to the pinchoff of the channel at the drain side. For the saturation voltage  $V_{SD,sat} = V_G - V_T$ , the saturation current is given by

$$I_{\rm SD,sat} = \mu C_{\rm i} \frac{W}{L} \frac{(V_{\rm G} - V_{\rm T})^2}{2} .$$

(2.61)

Eqn. 2.61 is usually applied for the mobility extraction of MISFET, plotting  $\sqrt{I_{SD,sat}}$  versus  $V_G$  and using the slope of the resulting linear function. However, since ZnO-based MISFET do not always show the ideal linear behavior of this plot, the obtained mobility is defective [Hof04]. In this case, it is better to use the saturation transconductance

$$g_{\rm m,sat} = \frac{\partial I_{\rm SD,sat}}{\partial V_{\rm G}} = \mu C_{\rm i} \frac{W}{L} (V_{\rm G} - V_{\rm T}) . \qquad (2.62)$$

The channel mobility is then given by

$$\mu_{\rm ch} = \frac{g_{\rm m,sat}}{\frac{W}{L}C_{\rm i}(V_{\rm G} - V_{\rm T})} \,. \tag{2.63}$$

# 2.4 Integrated Logic Circuits

Integrated circuits are the basis for today's complex electronics, e.g. computational devices (microchips), sensors, amplifiers etc. Integration of different electronic devices on a small area leads to manifold functionality and reduces fabrication costs. The first integrated circuit was developed by J. Kilby in 1958 [Kil76]. It was a hybrid flip-flop<sup>1</sup> consisting of two bipolar transistors on germanium substrate that were interconnected with gold wires. However, the first monolithic IC, i.e. fabricated on one single-crystalline substrate including transistors and interconnects, was patented in 1959 by R. Noyce [Noy61].

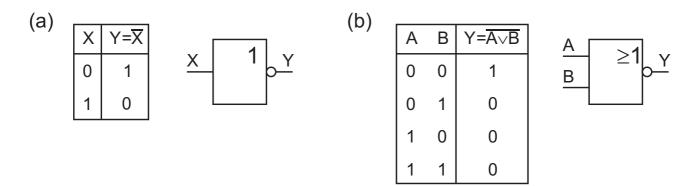

This thesis deals with two physical realizations of elements of the logic or Boolean algebra [Boo54]: the inverter and the NOR-gate. The truth tables and graphical symbols of these elements are shown in Fig. 2.6. With the help of Boole's laws, the logic elements "true" (1) and "false" (0) are linked together to more complex information. In circuits, this is realized by a high voltage level (true, 1) and a low level (false, 0). The basic logic element is the inverter (or NOT-gate). It is a device with one input and one output. the output is logic 1 only in the case, when the input is a logic 0 and vice versa. The NOR-gate represents the composed function "not-or". It is a device with two inputs and one output. The output gives the logic 1 only in the case, when none of the inputs are logic 1. It can be shown [Mor47], that it is possible to create a complete logic, e.g. including all possible statements, only by using NOR- and NOT-gates.

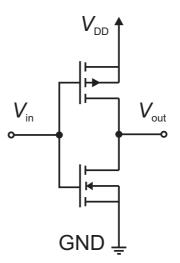

#### 2.4.1 Physical realization of the NOT function

In the most common realization (the CMOS<sup>2</sup>-technology), an inverter consists of one *n*-conducting MOSFET and one *p*-conducting MOSFET connected in series (Fig. 2.7). The transistors serve as complementary voltage-driven switches. The circuit is supplied with the voltage  $V_{DD}$ . If the input voltage  $V_{in}$  is low (logic 0), only the *p*-channel transistor is conducting; the output voltage equals the supply voltage  $V_{out} = V_{DD}$ , i.e. the output level is high (logic 1). For  $V_{in} > 0$  (typically > 1 V, logic

<sup>&</sup>lt;sup>1</sup>A flip-flop is a circuit that can switch and store two stable states.

<sup>&</sup>lt;sup>2</sup>Complementary Metal-Oxide-Semiconductor

Figure 2.6: Truth table and graphical symbol of a) a NOT-gate or inverter and b) a NOR-gate.

Figure 2.7: Circuit of a CMOS inverter.

1), the *n*-channel transistor is conducting and  $V_{DD}$  is grounded; i.e.  $V_{out} = 0$  V (logic 0). Since *n*-and *p*-type transistors are easily fabricated in silicon technology, this type of inverter is the basic for today's integrated circuitry.

A schematic voltage transfer curve (VTC) is depicted in Fig. 2.8. It serves as quantification of the inverter function and its figures of merit shall be defined in the following paragraphs.

In the ideal case, the resistances of the inverter's transistors are infinite if they are in the off-state, and equal to zero in the on-state. This would lead to the ideal VTC, where the output high level equals the supply voltage ( $V_{\text{OH}} = V_{\text{DD}}$ ) and the output low level is exactly zero ( $V_{\text{OL}} = 0$  V). The ideal inverter would switch at  $V_{\text{DD}}/2$ . The slope of the VTC would be infinite and the state of the inverter is uncertain only at this single point.

The real inverter is determined by the finite resistances of its transistors. So, there must be a transition range where the inverter switches from high to low level. The slope of this range equals to the gain of the inverter obtained if it was used as a voltage amplifier:

$$g = \left| \frac{\partial V_{\text{out}}}{\partial V_{\text{in}}} \right| \,. \tag{2.64}$$

Figure 2.8: Voltage-transfer curve of an ideal and a real inverter.

The maximum of g is denoted as peak gain magnitude (*pgm*). The input voltage, where *pgm* is achieved, is called reversal voltage  $V_{rev}$ . The borders of the transition range are marked with the input low and high voltages  $V_{IL}$  and  $V_{IH}$ , where g = 1.  $V_{IL}$  is the maximal input voltage for which the output level is clearly high. The other way around,  $V_{IH}$  is the minimal input voltage for which the output level is clearly low. Their difference is called uncertainty voltage range:

$$V_{\rm uc} = V_{\rm IH} - V_{\rm IL}$$

(2.65)

Left and right from the uncertainty voltage range are the regions for which the inverter output level is unambiguously defined. These regions are denoted as noise margins [Sed04]:

$$NM_{\rm L} = V_{\rm IL} - V_{\rm OL}, \qquad (2.66)$$

$$NM_{\rm H} = V_{\rm OH} - V_{\rm IH}.$$

(2.67)

For the ideal inverter, the noise margins would be equal and maximal  $NM_L = NM_H = V_{DD}/2$ . However, in the case of a non-ideal inverter, where g = 1 at two points of the input voltage, the noise margins would be ambiguous. Therefore J. Hauser suggested to maximize the product  $NM_L \times NM_H$ as figure of merit [Hau93].

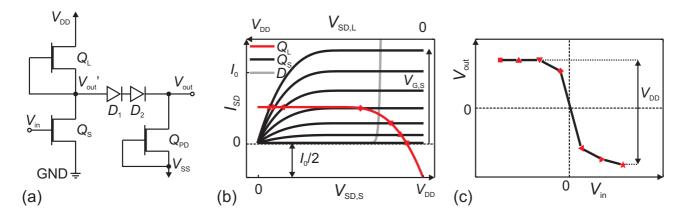

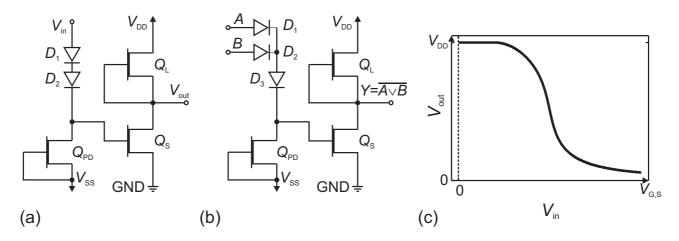

#### 2.4.2 MESFET-based inverter circuits

In the framework of this thesis, ZnO-MESFET-based inverter circuits were designed and fabricated. MESFET were used for the sake of their advantages, e.g. higher mobility and lower operation voltages, compared to MISFET. However, there are two constraints about ZnO-based MESFET: a) The

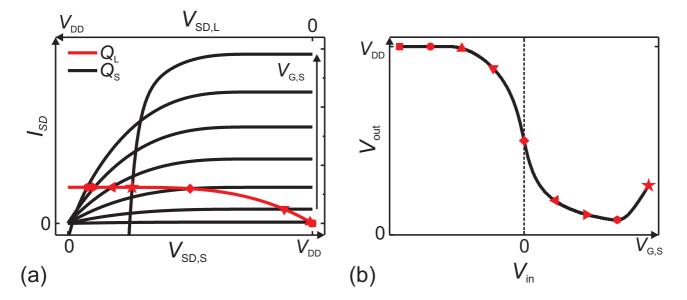

**Figure 2.9:** a) Circuit of a simple MESFET inverter, b) Output characteristics of the transistors, c) resulting voltage-transfer characteristic.

complementary design is not possible due to the absence of *p*-type transistors. b) The forward gatevoltage of a MESFET is restricted due to excessive gate leakage currents; an accumulation mode is not possible. Similar problems are known from the GaAs-MESFET technology. It has a five to ten times higher electron mobility compared to Si [Sed04] enabling the fabrication of transistors and circuits that can easily work in the GHz-range. But the hole mobility of GaAs is much lower, making *p*-type transistors and complementary circuits unattractive. The circuits used in this thesis were adopted from GaAs-MESFET logic described in [Sed04].

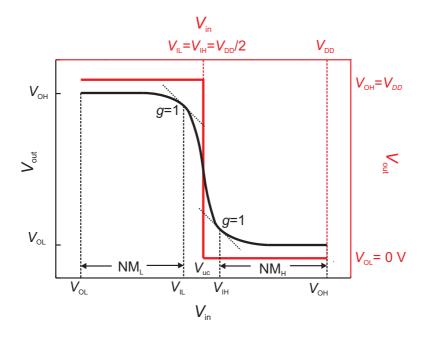

#### **Simple Inverter**

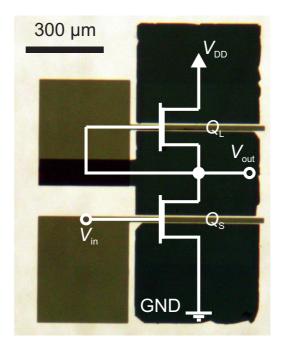

Figure 2.9a depicts the circuit of a simple MESFET inverter. Two normally-on MESFET are connected in series. The upper FET is denoted as load transistor  $Q_L$ , whereas the lower FET is the switching transistor  $Q_S$ . The source- and gate-contact of  $Q_L$  is shortcircuited. Thus, its gate voltage is constant  $V_{G,L} = 0$  V and the transistor is in the linear or saturation regime, respectively, depending on the operating voltage  $V_{DD}$  (which is related to the source-drain voltage  $V_{SD,L}$  of  $Q_L$ ). The state of  $Q_S$  can be controlled via the input voltage  $V_{in}$  (which is the gate voltage  $V_{G,S}$  of  $Q_S$ ).

The formation of the inverter's VTC is related to the transistor's output characteristics. Figure 2.9b shows the output characteristics of  $Q_S$  in the voltage range between 0 V and  $V_{DD}$  with  $V_{G,S}$  as parameter. In the same graph, the single output curve of  $Q_L$ , which is set to  $V_{G,L} = 0$  V, is drawn with reversed voltage axis. According to Kirchhoff's second law, the source-drain voltages are related to the operation voltage by

$$V_{\rm SD,S} + V_{\rm SD,L} = V_{\rm DD}$$

(2.68)

The intersection points of both characteristics represent the working points of the switching transistor, where both transistors carry the same current. With  $V_{SD,S} = V_{out}$ , these points reproduce the inverter's VTC (Fig. 2.9c). It can be seen, that it will be difficult to reach  $V_{out} = 0$  V, because then, the linear

Figure 2.10: a) Circuit and b) Characteristics of the transistors/diodes and c) the FET-logic inverter.

regime of the output characteristic of  $Q_S$ , has to be infinitely steep, i.e. the channel resistance has to be zero.

Since both transistor's resistances are equal at  $V_{G,S} = V_{G,L} = 0$  V, the switching point of the inverter is at  $V_{in} = 0$  V. This is, however, the central problem of the simple inverter whose output voltage  $V_{out}$ is always positive. For the high output of the inverter,  $V_{in}$  has to be  $V_{T,S} < V_{in} < 0$ , due to the higher resistance of  $Q_S$  in this voltage range. In order to turn  $Q_S$  off, the input voltage has to be lower than its turn-on voltage; i.e.  $V_{in} = V_{G,S} \le V_{T,S} < 0$ . If two or more inverters are connected in series, e.g. for a ring oscillator, the output of the subsequent inverter can never securely be logic high level, due to the first inverter's output is always positive. To circumvent this incompatibility, an additional level-shifting part has to be implemented into the circuit, as described in the following section.

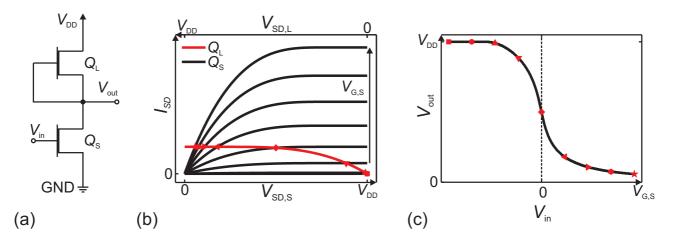

#### **FET-logic Inverter**

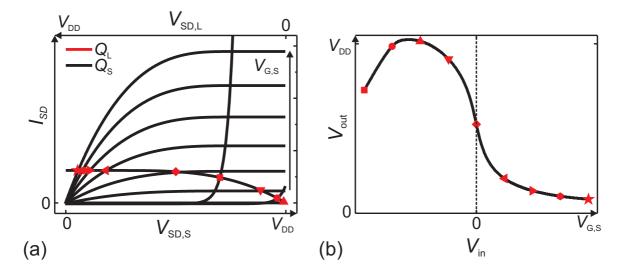

For the realization of inverter with level-shifter, the FET-logic (FL) is adopted from GaAs-MESFET technology. It was first developed by R. L. van Tuyl and C. A. Liechti in 1974 [Tuy74]. This logic family comprises additional Schottky diodes and transistors to adjust the voltage levels by means of the voltage drop over the diodes.

Figure 2.10a depicts the circuit of a FL-inverter consisting of the simple inverter part and the level shifter. The level shifter (LS) comprises two Schottky diodes  $D_1$  and  $D_2$  and an additional pull-down transistor  $Q_{PD}$  connected in series at the output of the simple inverter. The voltage drop across the two diodes lowers the former output level  $V'_{out}$  to  $V_{out} = V'_{out} - 2V_x$ , where  $V_x$  is the threshold voltage of the diode.  $Q_{PD}$  serves as constant-current supply for the diodes. To ensure that  $Q_{PD}$  is always in saturation, a negative  $V_{SS}$  with  $V_{SS} \ge V_{OL} + |V_T|$  is applied at its source contact. The pull-down transistor's gate width is chosen to be half of the gate widths of  $Q_L$  and  $Q_S$ . Furthermore,  $Q_{PD}$  provides the current to discharge a parasitic load capacity, when the inverter output level is low.

The VTC of the FL-inverter can be determined graphically analog the simple inverter (Fig. 2.9b and c). The corresponding graphs are given in Fig. 2.10b and c. For  $V_{in} = V_{G,S} < V_{T,S}$ ,  $Q_S$  is in the off-state; for  $V_{G,S} = 0$  V, the saturation current  $I_0$  flows. The current through  $Q_L$  is composed of the currents through  $Q_S$  and  $Q_{PD}$ , i.e.  $I_L = I_S + I_{PD}$ . Since the gate width of  $Q_{PD}$  is half of the other

**Figure 2.11:** a) Circuit of a Schottky-diode FET-logic (SDFL) inverter and b) a SDFL NOR-gate. c) Characteristic of a SDFL-inverter.

transistors' gate widths, its current is only half of the other currents (cf. Eqns. 2.48 and 2.52), i.e. the load transistor output characteristic is shifted to  $I_{\rm S} = I_{\rm L} - I_{\rm PD} = I_{\rm L} - I_0/2$ . Furthermore,  $V'_{\rm out}$  cannot exceed  $V_{\rm out} = 3V_{\rm x}$ , where  $V_{\rm out} = V_{\rm x}$  is the threshold voltage of the subsequent gate Schottky diode. Graphically, only the intersection points left of the three-diode characteristic are considered. The VTC of the FL-inverter is shifted towards negative output voltages (Fig. 2.10c). That means, the output low level is lower than the turn-on voltage of the subsequent inverter's gate, i.e.  $V_{\rm OL} < V_{\rm T,S}$  and secure inverter states are achieved.